УДК 681.32

### С.Ф. Тюрин

Пермский национальный исследовательский политехнический университет, Пермь, Россия

# ФУНКЦИОНАЛЬНО-ПОЛНЫЕ ТОЛЕРАНТНЫЕ ПОГИЧЕСКИЕ ЭЛЕМЕНТЫ ДЛЯ ОТКАЗОУСТОЙЧИВЫХ АВТОМАТИЗИРОВАННЫХ СИСТЕМ

Функционально-полные (в смысле критериев Поста) толерантные элементы были предложены как распространение парадигмы структурно-устойчивых ЭВМ, предложенной профессором В.А. Харитоновым на рубеже 90-х годов ХХ века, на уровень регистровых передач. Структурно-устойчивые ЭВМ обладают способностью к эмуляции требуемой системы команд при отказе отдельных команд из исходного множества. На эту идею натолкнула процедура покомандного диагностирования процессоров цифровых вычислительных комплексов специальных автоматизированных систем. В свою очередь, функционально-полные толерантные логические элементы (ФПТЛЭ) обладают способностью сохранения функциональной полноты при заданной модели отказов. В 1996-1997 годах были получены ФПТ функции с учетом модели однократных константных отказов одного из четырех входов соответствующего логического элемента (константа нуля и константа единицы). Они оказались композицией И, ИЛИ, НЕ логических функций. Из них практическое значение имеют известные функции 2ИЛИ-2И-НЕ, 2И-2ИЛИ-НЕ. При учете модели замыканий входов (Bridging Faults: Dominant; Wired AND, OR; Dominant AND/OR) оказалось, что мощность множества ФПТ функций уменьшается, но функции 2ИЛИ-2И-НЕ, 2И-2ИЛИ-НЕ сохраняют толерантность. В дальнейшем были рассмотрены вопросы сохранения функциональной полноты на транзисторном уровне для внутренних отказов логического элемента (вентиля) КМДП транзисторов (stuck-closed transistor - постоянно закрытый, stuck-open transistor - постоянно открытый). Показано, что функциональная полнота сохраняется при отказе одного транзистора либо в верхней части схемы (подключения «+» источника питания), либо в нижней (подключения шины «ноль вольт»). В дальнейшем пришло понимание, что аналогично можно обеспечивать сохранение не только функциональной полноты, но и самой реализуемой функции на уровне одного элемента. В статье рассматриваются особенности ФПТЛЭ, включенных в состав программных логистических интегральных систем (ПЛИС), имеющих так называемые LUT (look up table).

**Ключевые слова:** логический элемент, программные логистические интегральные системы (ПЛИС) типа FPGA, LUT, транзистор, функционально-полный толерантный логический элемент (ФПТЛЭ), избыточность, вероятность безотказной работы.

#### S.F. Tiurin

Perm National Research Polytechnic University, Perm, Russian Federation

# FUNCTIONAL COMPLETE TOLERANT LOGIC ELEMENTS FOR FAULT TOLERANT AUTOMATED SYSTEMS

Functional and complete (in the sense of Theorem Post) tolerant elements have been proposed as a paradigm spread structurally stable computers, proposed by Professor V.A. Kharitonov, at the turn of the 90s of the twentieth century, on the register transfer level. Structurally stable computers have the ability to emulate the desired command system in case of failure of individual teams from the original set. In turn, functionally complete tolerant logic elements FCTLE have the ability of maintaining the functional completeness of a given model of failures. In 1996-1997 FCT were obtained function model considering the constant failure of one of the four inputs of the corresponding element (stuck-at-0; stuck-at-1). They were the composition of AND, OR, NOT logic functions. Of these, the practical significance of known functions 2OR-2AND-NOT; 2AND-2OR-NOT. When adding Bridging Faults: (Dominant; Wired AND, OR; Dominant AND / OR), it proved that the cardinality of the set of functions FPT reduced, but 2OR-2AND-NOT; 2AND-2OR-NOT maintain tolerance. Then there were the issues of maintaining the functional completeness at the transistor level for internal failures logic element (valve) KMOS transistors (stuck-closed transistor - permanently closed, stuck-open transistor permanently open. It is shown that the functional completeness is preserved in case of failure of one transistor or a top of the circuit - connect "+" power supply or lower - bus connection "Ground". Then came the understanding that can be similar to conserve not only the functional completeness, but also the realization of a function at the level of a single element. The article features FCTLE elements included in the FPGA with the so-called LUT (look up table).

**Keywords:** FPGA, logic functions, logic element, LUT, transistor, redundancy, functional complete tolerant logic element (FCTLE), reliabilities.

#### Введение

Функционально-полные толерантные логические элементы явились развитием концепции структурной устойчивости профессора В.А. Харитонова [1]. ФПТЛЭ сохраняют логический базис при отказах в рамках заданной модели в смысле знаменитой теоремы Поста [2, 3] как альтернатива внутреннего резервирования внешнему. В отличие от базисов И-НЕ, ИЛИ-НЕ, ФПТЛЭ используют комбинирование операций И-НЕ, ИЛИ-НЕ. Таким образом, речь идет об активной отказо-устойчивости, при которой остаточные базисы могут быть использованы для восстановления требуемой функции. Для этого необходима возможность реконфигурации схем из таких элементов, что реализовано в программируемых пользователем вентильных матрицах ППВМ – программируемых логических интегральных схемах типа FPGA. Пред-

$<sup>^{1}</sup>$  Функционально-полный толерантный элемент: пат. № 2438234 Рос. Федерация / С.Ф. Тюрин, О.А. Громов. Опубл. 27.12.2011. Бюл. № 36.

полагается, что имеются средства (встроенные или внешние) обнаружения факта отказа и определения конкретного состояния ФПТЛЭ. Сама идея развивалась также направлением самосинхронных автоматов [4–8] на базе Института проблем информатики (ИПИ) РАН [9, 10].

В дальнейшем были исследованы соответствующие ФПТ логические функции с учетом модели замыканий входов, множество которых оказалось подмножеством множества ФПТ функций, полученных в работе [2]. Однако для пассивной отказоустойчивости АСУ целесообразнее сохранять исходную базисную функцию, что и было предложено в статье [3], это уже требует значительной избыточности.

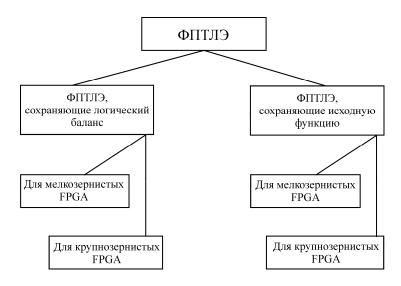

Таким образом, ФПТЛЭ можно разделить на ФПТ, сохраняющие базис в смысле теоремы Поста, и ФПТ, сохраняющие исходную функцию. И те, и другие (по классификации ПЛИС) мелкозернистые и крупнозернистые [11] (рис. 1).

Рис. 1. Классификация ФПТЛЭ

В дальнейшем были получены ФПТЛЭ для парирования кратных отказов. Рассмотрим особенности вариантов ФПТЛЭ, парирующих в указанных выше смыслах однократные отказы.

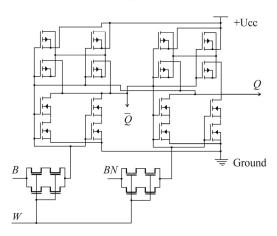

## 1. КМДП-реализация ФПТЛЭ для мелкозернистых ПЛИС

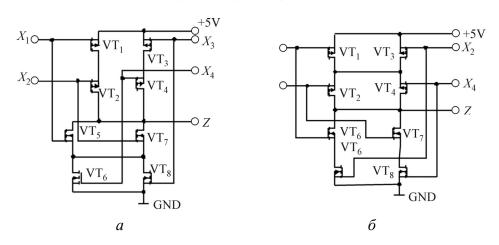

При модели отказов одного КМДП-транзистора или входа функциональная полнота сохраняется. Например, для КМДП-структур

2ИЛИ-2И-НЕ, 2И-2ИЛИ-НЕ – это функции  $\overline{x}_1\overline{x}_2 \vee \overline{x}_3\overline{x}_4$  и  $\overline{x}_2\overline{x}_4 \vee \overline{x}_3\overline{x}_4 \vee \overline{x}_1\overline{x}_4 \vee \overline{x}_2\overline{x}_3 = (\overline{x}_1 \vee \overline{x}_2)(\overline{x}_3 \vee \overline{x}_4)$  (рис. 2).

Рис. 2. КМДП-схемы ФПТЛЭ, сохраняющих базис FCTLE1 (a) и FCTLE2 ( $\delta$ ) на основе КМДП-транзисторов VT1–VT8

Схемы на рис. 2 [3] характеризуются наличием двух подсхем – подключения источника питания (z+) и двойственной ей схемы подключения шины «ноль вольт» (z-), которые описываются выражениями:

$$Z_{+FCT1} = \overline{x}_1 \overline{x}_2 \vee \overline{x}_3 \overline{x}_4; \tag{1}$$

$$Z_{-FCT1} = (\overline{x}_1 \vee \overline{x}_2)(\overline{x}_3 \vee \overline{x}_4); \tag{2}$$

$$Z_{+FCT2} = (\overline{x}_1 \vee \overline{x}_2)(\overline{x}_3 \vee \overline{x}_4); \tag{3}$$

$$Z_{-FCT2} = x_1 x_2 \vee x_3 x_4. \tag{4}$$

Несмотря на то что при отказах нарушается ортогональность функций (z+), (z-), т.е. на некоторых наборах одновременно могут быть подключены либо обе шины, либо ни одной, чего не должно быть при нормальном функционировании, всегда возможно путем подбора настроить элемент на реализацию остаточного базиса, в отличие от эквивалентного по числу транзисторов элемента 4И-НЕ. Причем возможны два отказа – отказ транзистора в (z+) и отказ транзистора в (z-). Таким образом, отказы транзисторов практически кратные.

Для сохранения базисной функции 2ИЛИ-НЕ  $\overline{x}_1\overline{x}_2$  при модели однократных константных отказов необходимо выражение

$$\overline{x}_1 \overline{x}_2 \overline{x}_3 \overline{x}_4 \vee \overline{x}_5 \overline{x}_6 \overline{x}_7 \overline{x}_8.$$

(5)

Легко видеть, что в случае четырхкратной избыточности

$$\overline{x}_{1,1}\overline{x}_{2,1}\overline{x}_{1,2}\overline{x}_{2,2} \vee \overline{x}_{1,3}\overline{x}_{2,3}\overline{x}_{1,4}\overline{x}_{2,4} \tag{6}$$

функция 2ИЛИ-НЕ  $\bar{x}_1\bar{x}_2$  сохранится при любом однократном константном отказе.

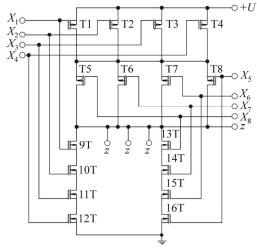

Такой элемент<sup>2</sup> [3], содержащий 16 КМДП-транзисторов, может быть использован как сложный (восемь переменных):

$$f = \overline{x}_1 \overline{x}_2 \overline{x}_3 \overline{x}_4 \vee \overline{x}_5 \overline{x}_6 \overline{x}_7 \overline{x}_8 \tag{7}$$

при условии отсутствия отказов и отказоустойчивый (две переменные) – в специальной аппаратуре автоматизированных систем управления (АСУ). Для сохранения базисной функции 2И-НЕ  $\overline{x}_1 \vee \overline{x}_2$  при модели однократных константных отказов может быть использован элемент

$$(\overline{x}_1 \vee \overline{x}_2 \vee \overline{x}_3 \vee \overline{x}_4)(\overline{x}_5 \vee \overline{x}_6 \vee \overline{x}_7 \vee \overline{x}_8),$$

(8)

T.e.

$$\left(\overline{x}_{1,1} \vee \overline{x}_{2,1} \vee \overline{x}_{1,2} \vee \overline{x}_{2,2}\right) \left(\overline{x}_{1,3} \vee \overline{x}_{2,3} \vee \overline{x}_{1,4} \vee \overline{x}_{2,4}\right). \tag{9}$$

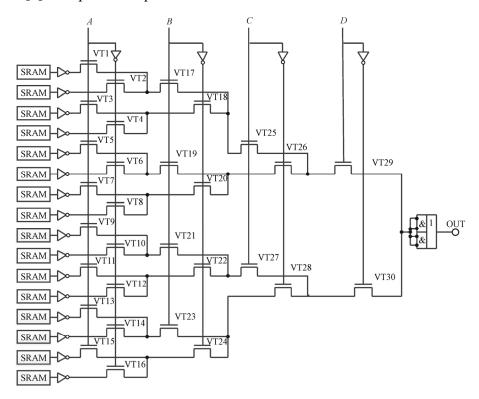

КМДП-реализация показана на рис. 3.

Рис. 3. КМДП-схема ФПТЛЭ, сохраняющего функцию 2И-HE-FCTLE4 –  $(\overline{x}_1 \vee \overline{x}_2 \vee \overline{x}_3 \vee \overline{x}_4)(\overline{x}_5 \vee \overline{x}_6 \vee \overline{x}_7 \vee \overline{x}_8) \ z_{0\nu} = x_1 x_2 x_3 x_4 \vee x_5 x_6 x_7 x_8$

$<sup>^2</sup>$  Функционально-полный толерантный элемент: пат. № 2438234 Рос. Федерация / С.Ф. Тюрин, О.А. Громов. Опубл. 27.12.2011. Бюл. № 36.

# 2. КМДП-реализация ФПТЛЭ, сохраняющих базис, для крупнозернистых ПЛИС

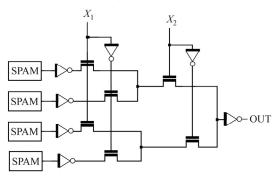

Простейший LUT [12, 13] на две переменные (2-LUT) имел бы вид, представленный на рис. 1.

LUT на две переменные (рис. 4) реализует функцию

$$z_{\text{OUT}} = a\overline{x}_2\overline{x}_1 \lor b\overline{x}_2x_1 \lor cx_2\overline{x}_1 \lor dx_2x_1, \tag{10}$$

где a, b, c, d — настройки, записываемые в ячейки статической оперативной памяти SRAM (снизу вверх).

Рис. 4. LUT на две переменные (2-LUT)

Для настройки на заданную логическую функцию двух переменных в четыре ячейки ОЗУ (SRAM) загружается соответствующая таблица истинности. При активации одного из четырех путей в дереве транзисторов (см. рис. 4) переменными  $X_1$ ,  $X_2$  значение логической функции считывается из соответствующей ячейки ОЗУ и передается на выход ОИТ. Инверторы по переменным обеспечивают реализацию всех членов совершенной дизъюнктивной нормальной формы (СДНФ). LUТ на три переменные (3-LUT) представлен на рис. 5.

Рис. 5. LUT на три переменные (3-LUT)

Здесь уже необходимо 8 бит настройки:

$$z_{\text{OUT}} = a\overline{x}_{3}\overline{x}_{2}\overline{x}_{1} \lor b\overline{x}_{3}\overline{x}_{2}x_{1} \lor c\overline{x}_{3}x_{2}\overline{x}_{1} \lor d\overline{x}_{3}x_{2}x_{1} \lor$$

$$\lor ex_{3}\overline{x}_{2}\overline{x}_{1} \lor fx_{3}\overline{x}_{2}x_{1} \lor gx_{3}x_{2}\overline{x}_{1} \lor hx_{3}x_{2}x_{1}. \tag{11}$$

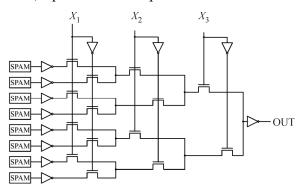

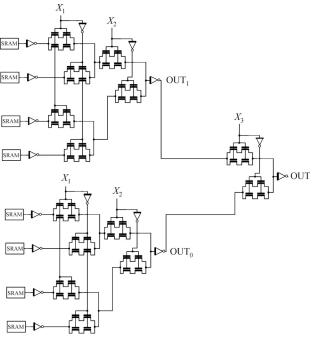

В источниках указано, что оптимальным по быстродействию и сложности представления типовых логических функций является использование LUT на четыре переменных (4-LUT). Такой LUT для входных переменных A, B, C, D (настройка – 16 бит) с установленным на выходе функционально-полным толерантным логическим элементом [3] изображен на рис. 6.

Рис. 6. LUT на четыре переменные (4-LUT) с ФПТЛЭ на выходе, настроенным на реализацию инверсии

Такой LUT для входных переменных A, B, C, D обеспечивает работоспособность в объеме своих «половинных» возможностей при отказе одного любого входа A, B, C, D, либо одного транзистора в дереве передающих транзисторов VT1–VT30, либо в элементах-инверторах,

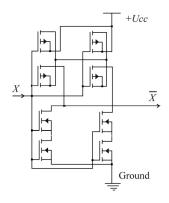

Рис. 7. ФПТЛЭ-инвертор с функцией  $(x \lor x)(x \lor x)$

Такие ФПТЛЭ-инверторы, использующие так называемое расчетверение, могут быть установлены и вместо входных инверторов LUT, и вместо инверторов по данным. Для обнаружения ошибок при вычислении логических функций в LUT целесообразно использовать дополнительные средства контроля и диагностики.

# 3. КМДП реализация ФПТЛЭ, сохраняющих исходную функцию, для крупнозернистых ПЛИС

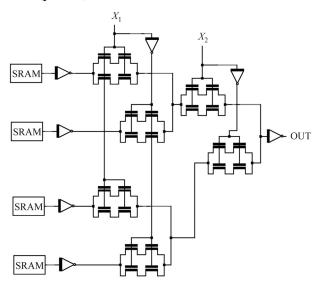

Дальнейшее увеличение избыточности возможно путем резервирования передающих транзисторов (расчетверения передающих транзисторов). Однако непосредственно для 4-LUT это не может быть выполнено в силу ограничений Мида и Конвей на число последовательно соединенных транзисторов [14, 15], поэтому вначале обеспечим резервирование 2-LUT (рис. 8).

Рис. 8. Отказоустойчивый LUT на две переменные (2-LUT-FT)

На рис. 8 используется ФПТ передающая функция  $xx \lor xx$ , где x – передающие транзисторы. Тогда схема толерантна к отказу любого одного транзистора в каждой четверке. Для обеспечения толерантности SRAM предложена ячейка [3] (рис. 9).

Рис. 9. Отказоустойчивая SRAM

Для получения 3-LUT-FT предлагается схема, представленная на рис. 10.

Рис. 10. Отказоустойчивый LUT на три переменные (3-LUT-FT)

Соединение двух 3-LUT-FT через указанный на рис. 10 1-LUT-FT позволяет получить требуемый 4-LUT-FT.

Для получения n LUT (n > 4) на базе 4-LUT, содержащего 30 транзисторов в дереве и два транзистора в выходном инверторе 4-LUT, при соединении двух 4-LUT парой передающих транзисторов с инвертором необходима сложность

$$L_{n.4} = 2^{n} \cdot 8 + 32 \cdot 2^{n-4} + 4(2^{n-4} - 1) + 2n, \tag{12}$$

где  $2^n \cdot 8$  — сложность настройки на реализацию заданной логической функции (в числе транзисторов); 8 — суммарное число транзисторов в SRAM (6 шт.) и соответствующем инверторе (2 шт.);  $32 \cdot 2^{n-4}$  — число транзисторов в требуемых 4-LUT без учета инверторов по входам переменных;  $4(2^{n-4}-1)$  — сложность требуемых дополнительных 1-LUT при n > 4; 2n — число транзисторов в инверторах входных переменных без учета ограничений по нагрузочной способности инверторов по входам.

В свою очередь, для получения n LUT-FT требуется «расчетверить» каждый транзистор:

$$L_{n.4-ft} = 4 \left[ 2^n \cdot 8 + 32 \cdot 2^{n-4} + 4 \left( 2^{n-4} - 1 \right) + 2n \right]. \tag{13}$$

Таблица 1

### 4. Оценка вероятности безотказной работы 4-LUT и 4-LUT-FT

Затраты на реализацию 4-LUT (см. рис. 6) представлены в табл. 1.

Затраты на реализацию 4-LUT

| <b>№</b><br>п/п | Наименование                   | Количество транзисторов, шт. |

|-----------------|--------------------------------|------------------------------|

| 1               | Дерево передающих транзисторов | 30                           |

| 2               | Инверторы – 21 шт.             | 42                           |

| 3               | Шеститранзисторная SRAM        | 96                           |

|                 | Итого                          | 168                          |

Затраты на реализацию 4-LUT-FT (см рис. 10) представлены в табл. 2.

Таблица 2 Затраты на реализацию 4-LUT-FT

| №<br>п/п | Наименование                   | Количество транзисторов |

|----------|--------------------------------|-------------------------|

| 1        | Дерево передающих транзисторов | 120                     |

| 2        | Инверторы – 16 + 8 + 8 + 2     | 272                     |

| 3        | Шеститранзисторная SRAM        | 384                     |

|          | Итого                          | 776                     |

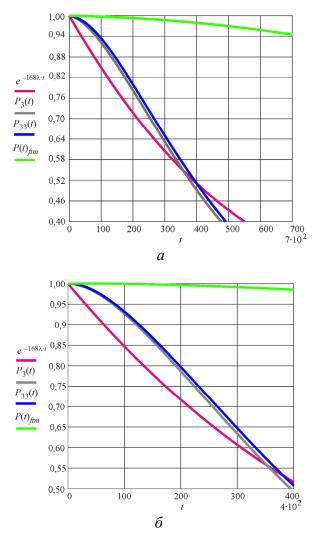

Получим выражения вероятности безотказной работы 4-LUT - P(t) и  $4\text{-LUT-FT} - P(t)_{ftm}$  с учетом экспоненциальной модели отказов, задавая интенсивность отказов одного транзистора и время работы (рис. 11):

$$P(t) = e^{-(168)\cdot\lambda \cdot t},$$

$$P(t)_{fim} = \left[e^{-(4)\cdot\lambda \cdot t} + 4 \cdot e^{-3\cdot\lambda \cdot t} \left(1 - e^{-1\cdot\lambda \cdot t}\right)\right]^{30} \cdot \left[e^{-(4)\cdot\lambda \cdot t} + 4 \cdot e^{-3\cdot\lambda \cdot t} \left(1 - e^{-1\cdot\lambda \cdot t}\right)\right]^{68} \times \left[e^{-(4)\cdot\lambda \cdot t} + 4 \cdot e^{-3\cdot\lambda \cdot t} \left(1 - e^{-1\cdot\lambda \cdot t}\right)\right]^{96}.$$

$$(14)$$

$$P(t)_{fim} = \left[e^{-(4)\cdot\lambda \cdot t} + 4 \cdot e^{-3\cdot\lambda \cdot t} \left(1 - e^{-1\cdot\lambda \cdot t}\right)\right]^{96}.$$

$$(14)$$

$$P(t)_{fim} = \left[e^{-(4)\cdot\lambda \cdot t} + 4 \cdot e^{-3\cdot\lambda \cdot t} \left(1 - e^{-1\cdot\lambda \cdot t}\right)\right]^{96}.$$

$$0,91$$

$$0,82$$

$$0,73$$

$$0,28$$

$$0,19$$

$$0,10$$

$$0 = 100 = 200 = 300 = 400 = 500 = 600 = 700$$

$$7 \cdot 10^{2}$$

Рис. 11. Графики изменения вероятности безотказной работы 4-LUT – P(t) и 4-LUT-FT –  $P(t)_{fim}$  при интенсивности отказов  $\lambda = 10^{-5}$  1/ч

Сравним предложенное резервирование с троированием, сложность мажоритарного элемента на выходе 4-LUT равна 12 транзисторам:

$$P(t)_3 = \left[3 \cdot e^{-2 \cdot (168) \cdot \lambda \cdot t} - 2 \cdot e^{-3 \cdot (168) \cdot \lambda \cdot t}\right] \cdot e^{-12 \cdot \lambda \cdot t}.$$

(15)

Сравним предложенное резервирование с троированием, использующим три мажоритарных элемента на выходе 4-LUT:

$$P(t)_{3,3} = \left[3 \cdot e^{-2 \cdot (168) \cdot \lambda \cdot t} - 2 \cdot e^{-3 \cdot (168) \cdot \lambda \cdot t}\right] \cdot \left[3 \cdot e^{-2 \cdot (12) \cdot \lambda \cdot t} - 2 \cdot e^{-3 \cdot (12) \cdot \lambda \cdot t}\right]. \quad (16)$$

Соответствующие графики изображены на рис. 12.

Рис. 12. Графики изменения вероятности безотказной работы: a – в диапазоне от 1 до 0,4, схемы 4-LUT без резервирования P(t);  $\delta$  – в диапазоне от 1 до 0,5, вероятности безотказной работы резервированной схемы с расчетверением  $P(t)_{fim}$ , вероятности безотказной работы резервированной троированной схемы с одним мажоритаром  $P_3$  и троированной схемы с тремя мажоритарами  $P_{33}$  при интенсивности отказов (сбоев)  $\lambda = 10^{-5}$  1/ч

### Выводы

Таким образом, использование ФПТЛЭ позволяет сохранять логический базис как в мелкозернистых, так и в крупнозернистых ПЛИС АСУ при отказе одного любого транзистора, одного любого входа. При таких неисправностях есть возможность использования «половинных» возможностей элемента, а массив «пораженнных» элементов после диагностики и реконфигурации обеспечивает синтез не всех, но наиболее важных функций АСУ.

Введение существенной избыточности позволяет получить ФПТЛЭ, сохраняющих логическую функцию при отказах одного транзистора в каждой четверке транзисторов. Подобное расчетверение позволяет получить более высокую вероятность безотказной работы, чем троирование. При этом затраты на троирование равны 516 транзисторам с учетом одного мажоритара либо 540 – с учетом трех мажоритаров. Затраты на реализацию предлагаемого ФПТЛЭ с сохранением логической функции с учетом декомпозиции 4-LUT для удовлетворения требований Мида и Конвей равны 776 транзисторам, что примерно на 50 % больше по сравнению с затратами на троирование.

Предложенные ФПТЛЭ могут быть использованы в так называемых адаптивных логических модулях АЛМ [16–19] для RHBD (radiation hardering by design) процессорах и устройствах АСУ, обеспечивающих радиационную стойкость посредством архитектурных решений [20].

### Список литературы

- 1. Харитонов В.А., Тюрин С.Ф. Модели управления устойчивостью функционально избыточных систем // Управление большими системами: материалы Междунар. науч.-практ. конф. М., 1997. С. 266.

- 2. Тюрин С.Ф. Проблема сохранения функциональной полноты булевых функций при «отказах» аргументов // Автоматика и телемеханика. 1999. № 9. С. 176–186.

- 3. Tyurin S.F., Grekov A.V. Functionally complete tolerant elements // International Journal of Applied Engineering Research. 2015. Vol. 10, N 14. P. 34433–34442.

- 4. Muller D.E., Bartky W.S. A theory of asynchronous circuits // Proc. Int. Symp. on the Theory of Switching. Harvard University Press, 1959. Part 1. P. 204–243.

- 5. Апериодические автоматы / под ред. В.И. Варшавского. М.: Наука, 1976. 304 с.

- 6. Искусственный интеллект. Т. 3. Программные и аппаратные средства / В.И. Варшавский, В.Б. Мараховский, Л.Я. Розенблюм, А.В. Яковлев; под ред. В.Н. Захарова, В.Ф. Хорошевского. М.: Радио и связь, 1990. 304 с.

- 7. Delay-insensitive asynchronous ALU for cryogenic temperature environments / B. Hollosi [et al.] // Circuits and Systems. 2008. P. 322–325.

- 8. Yakovlev A. Energy-modulated computing // Design, Automation & Test in Europe Conference & Exhibition (DATE). 2011. P. 1–6.

- 9. Плеханов Л.П. Основы самосинронных электронных схем [Электронный ресурс]. URL: https://www.docme.ru/doc/997042/osnovy-samosinhronnyh-e-lektronnyh-shem.-%E2%80%94-e-l.-izd (дата обращения: 01.11.2015).

- 10. Библиотека элементов для проектирования самосинхронных полузаказных микросхем серий 5503/5507 и 5508/5509 / Ю.А. Степченков, А.Н. Денисов, Ю.Г. Дьяченко, Ф.И. Гринфельд, О.П. Филимоненко, Н.В. Морозов, Д.Ю. Степченков. М.: ИПИ РАН, 2008. 296 с.

- 11. Угрюмов Е.П. Цифровая схемотехника: учеб. пособие. СПб.: БХВ-Петербург, 2004. 518 с.

- 12. Строгонов А., Цыбин С. Программируемая коммутация ПЛИС: взгляд изнутри [Электронный ресурс]. URL: http://www.kit-e.ru/articles/plis/ 2010\_11\_56.php (дата обращения: 16.12.2014).

- 13. Основные производители современных ПЛИС-компьютеров и комплектующих к ним [Электронный ресурс]. URL: https://parallel.ru/fpga/vendors.html (дата обращения: 29.10.2015).

- 14. Ульман Дж.Д. Вычислительные аспекты СБИС / пер. с англ. А.В. Неймана / под ред. П.П. Пархоменко. М.: Радио и связь, 1990. 480 с.

- 15. Глебов А.Л. SP-BDD модель цифровых КМОП-схем и ее приложения в оптимизации и моделировании // Информационные технологии. 1997. N 10. C. 44.

- 16. Золотуха Р., Комолов Д. Stratix III новое семейство FPGA фирмы Altera [Электронный ресурс]. URL: http://kit-e.ru/assets/files/pdf/2006\_12\_30.pdf (дата обращения: 28.11.2015).

- 17. Строгонов А., Цыбин С. Использование ресурсов ПЛИС Stratix III фирмы Altera при проектировани микропроцессорных ядер

[Электронный ресурс]. – URL: file:///C:/Users/%D0%A2%D1%8E%D1%80%D0%B8%D0%BD/Desktop/%D0%A6%D1%8B%D0%B1%D0%B8%D0%BD%2010%20%D0%B3%D0%BE%D0%B4.pdf (дата обращения: 27.11.2015).

- 18. Peter ClarkeCEO Interview: John Lofton Holt of Achronix Fastest FPGA? URL: http://www.eetimes.com/document.asp?doc\_id=1271406 (дата обращения: 29.10.2015).

- 19. Speedster22i configuration user guide [Электронный ресурс]. URL: http://www.achronix.com/wp-content/uploads/docs/Speedster22i\_Configuration\_User\_Guide\_UG033.pdf (дата обращения: 29.10.2015).

- 20. Чекмарев С.А. Способ и система инъекции ошибок для тестирования сбоеустойчивых процессоров бортовых систем космических аппаратов [Электронный ресурс] // Вестник Сибир. гос. аэрокосм. ун-та им. акад. М.Ф. Решетнева. -2014. -№ 4 (56). URL: http://cyberleninka.ru/article/n/sposob-i-sistema-inektsii-oshibok-dlya-testirovaniya-sboeustoychevyh-protsessorov-bortovyh-sistem-kosmicheskih-apparatov (дата обращения: 16.12.2015).

#### References

- 1. Kharitonov V.A., Tiurin S.F. Modeli upravleniia ustoichivost'iu funktsional'no izbytochnykh system [Models of management stability functionally redundant systems]. *Materialy Mezhdunarodnoi nauchno-prakticheskoi konferentsii "Upravlenie bol'shimi sistemami"*. Moscow, 1997, p. 266.

- 2. Tiurin S.F. Problema sokhraneniia funktsional'noi polnoty bulevykh funktsii pri "otkazakh" argumentov [Retention of functional completeness of Boolean functions under "failures" of the arguments]. *Avtomatika i telemekhanika*, 1999, no. 9, pp. 176-186.

- 3. Tiurin S.F., Grekov A.V. Functionally complete tolerant elements [Functionally complete tolerant element]. *International Journal of Applied Engineering Research*, 2015, vol. 10, no. 14, pp. 34433-34442.

- 4. Muller D.E., Bartky W.S. A theory of asynchronous circuits. *Proceedings of International Symposium on the Theory of Switching*, part 1. Harvard University Press, 1959, pp. 204–243.

- 5. Aperiodicheskie avtomaty [Aperiodic machines: under edition by V.I. Varshavskii]. Ed. by V.I. Varshavskii. Moscow: Nauka, 1976. 304 p.

- 6. Varshavskii V.I., Marakhovskii V.B., Rozenblium L.Ia., Iakovlev A.V. Iskusstvennyi intellect. Vol. 3. Programmye i apparatnye sredstva

[Aperiodic circuitry in book artificial intelligent. Vol. 3. Software and hardware]. Moscow: Radio i sviaz', 1990. 304 p.

- 7. Hollosi B. [et al.]. Delay-insensitive asynchronous ALU for cryogenic temperature environments. *Circuits and Systems*, 2008, pp. 322-325.

- 8. Yakovlev A. Energy-modulated computing. *Design, Automation & Test in Europe Conference & Exhibition (DATE)*, 2011. pp. 1-6.

- 9. Plekhanov L.P. Osnovy samosinronnykh elektronnykh skhem [Basic of the self-timed circuits], available at: https://www.docme.ru/doc/997042/osnovy-samosinhronnyh-e-lektronnyh-shem.-%E2%80%94-e-l.-izd (accessed 01 November 2015).

- 10. Stepchenkov Iu.A., Denisov A.N., D'iachenko Iu.G., Grinfel'd F.I., Filimonenko O.P., Morozov N.V., Stepchenkov D.Iu. Biblioteka elementov dlia proektirovaniia samosinkhronnykh poluzakaznykh mikroskhem serii 5503/5507 i 5508/5509 [Library elements for designing self-timed chip series 5503/5507 and 5508/5509]. Moscow, 2008. 296 p.

- 11. Ugriumov E.P. Tsifrovaia skhemotekhnika [Digital circuity]. Saint Petersburg: BKhV-Peterburg, 2004. 518 p.

- 12. Strogonov A., Tsybin S. Programmiruemaia kommutatsiia PLIS: vzgliad iznutri [Programmable switching FPGA: inside view], available at: http://www.kit-e.ru/articles/plis/2010\_11\_56.php (accessed 16 December 2014).

- 13. Osnovnye proizvoditeli sovremennykh PLIS-komp'iuterov i komplektuiushchikh k nim [The main producers of advanced FPGA-based computers and accessories], available at: https://parallel.ru/fpga/vendors.html (accessed 29 October 2015).

- 14. Ul'man Dzh.D. Vychislitel'nye aspekty SBIS [Computational aspects of VLSI]. Moscow: Radio i sviaz', 1990. 480 p.

- 15. Glebov A.L. SP-BDD-model' tsifrovykh KMOP-skhem i ee prilozheniia v optimizatsii i modelirovanii [SP-BDD model of digital CMOS circuits and its applications in optimization and simulation]. *Informatsionnye tekhnologii*, 1997, no. 10, p. 44.

- 16. Zolotukha R., Komolov D. Stratix III novoe semeistvo FPGA firmy Altera [Stratix III a new family of FPGA from Altera], available at: http://kit-e.ru/assets/files/pdf/2006\_12\_30.pdf (accessed 28 November 2015).

- 17. Strogonov A., Tsybin S. Ispol'zovanie resursov PLIS Stratix III firmy Altera pri proektirovani mikroprotsessornykh iader [Resource use Stratix III FPGA from Altera the design of microprocessor cores], available

at: http://www.kit-e.ru/articles/plis/2010\_2\_39.php (accessed 27 November 2015).

- 18. Peter Clarke CEO Interview: John Lofton Holt of Achronix Fastest FPGA?, available at: http://www.eetimes.com/document.asp?doc\_id=1271406 (accessed 29 October 2015).

- 19. Speedster22i configuration user guide, available at: http://www.achronix.com/wp-content/uploads/docs/Speedster22i\_Configuration\_User\_Guide\_UG033.pdf (accessed 29 October 2015).

- 20. Chekmarev S.A. Sposob i sistema in"ektsii oshibok dlia testirovaniia sboeustoichivykh protsessorov bortovykh sistem kosmicheskikh apparatov [Method and system for testing the error injection sboeustoychivyh processors onboard spacecraft systems]. *Vestnik Sibirskogo gosudarstvennogo aerokosmicheskogo universiteta imeni akademika M.F. Reshetneva*, 2014, vol. 56, iss. 4, available at: http://cyberleninka.ru/article/n/sposob-i-sistema-inektsii-oshibok-dlya-testirovaniya-sboeustoychevyh-protsessorov-bortovyh-sistem-kosmicheskih-apparatov (accessed 29 December 2015).

Получено 18.08.2016

### Об авторе

**Тюрин Сергей Феофентович** (Пермь, Россия) – доктор технических наук, профессор кафедры «Автоматики и телемеханики», Пермский национальный исследовательский политехнический университет, заслуженный изобретатель Российской Федерации (614990, Пермь, Комсомольский пр., 29, e-mail: tyurinsergfeo@yandex.ru).

### About the author

**Sergei F. Tiurin** (Perm, Russian Federation) – Doctor of Technical Sciences, Professor, Department of Automation and Telemechanics, Perm National Research Polytechnic University, Honored Inventor of the Russian Federation (29, Komsomolsky av., Perm, 614990, Russian Federation, e-mail: tyurinsergfeo@yandex.ru).