2017 Электротехника, информационные технологии, системы управления

No 23

УДК 004.312

## **Р.В.** Вихорев<sup>1</sup>, С.Ф. Тюрин<sup>2</sup>

<sup>1</sup>ПАО «Пермская научно-производственная приборостроительная компания», Пермь, Россия

# ПРОГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ ПЛИС FPGA ДЛЯ РЕАЛИЗАЦИИ СИСТЕМ ЛОГИЧЕСКИХ ФУНКЦИЙ

Исследована архитектура программируемых логических интегральных схем, в основе которой использована Look-Up Table. Описана существующая проблема программируемых логических интегральных схем типа field programmable gate array, которая заключается в неориентированности логических элементов, базирующихся на LUT на системную реализацию логических функций. В статье описывается LUT на одну переменную, дается его характеристика, описывается реализация ортогональности сигналов в ветвях дерева передающих транзисторов. Предлагается усовершенствованный метод реализации в field programmable gate array систем логических функций, заданных в совершенной дизъюнктивной нормальной форме, основанный на передаче сигнала в другом направлении. Предлагается элемент DC-LUT, приводится подробное описание структуры, а также его характеристика. Реализацию систем логических функций обеспечивает блок дизъюнкций конституент логической функции, описание которого так же приводится. Для реализации функций большого числа переменных предлагается новый ДНФ-LUT. Описывается усовершенствованная структура нового ДНФ-LUT, модификация которого заключается в том, что выполнена адаптация к уровню передающих транзисторов, используемых в LUT, и применено оригинальное кодирование конъюнкций в дизъюнктивной нормальной форме. Рассматривается программирование одной переменной для предлагаемой структуры ДНФ-LUT. Делается вывод о целесообразности применения усовершенствованных методов для реализации систем логических функций в программируемых логических интегральных схемах типа field programmable gate array.

**Ключевые слова**: программируемые логические интегральные схемы, field programmable gate array, Look-Up Table, системы логических функций, DC-LUT, ДНФ-LUT.

### R.V. Vikhorev, S.F. Tyurin

Public joint stock "Perm scientific industrial instrument-making company",

Perm, Russian Federation

Perm National Research Polytechnic University, Perm, Russian Federation

## PROGRAMMABLE LOGIC ELEMENTS OF FPGA FOR REALIZATION SYSTEM OF LOGICAL FUNCTIONS

The article introduces the research of the architecture of programmable logic integrated circuits based on the Look-Up Table. There is described the existing problem of programmable logic integrated circuits of the type field programmable gate array, which consists in the lack of orientation of logic elements based on LUT to the system implementation of logic functions. The article describes in detail LUT with one

<sup>&</sup>lt;sup>2</sup>Пермский национальный исследовательский политехнический университет, Пермь, Россия

variable, characterizes it, reports the realization of orthogonality of signals in the branches of the tree of transistors. There is proposed an improved method of implementation systems of logical functions defined in a perfect disjunctive normal form in the field programmable gate array based on signal transmission in the other direction. The DC-LUT element is offered, a detailed description of the structure is given, as well as its characteristic. Realization of systems of logic functions is provided by a block of disjunctions of the constituent of a logical function, its description is also given. A new DNF-LUT is proposed for implementation the functions of a large number of variables. There is described an improved structure of the new DNF-LUT modification, which consists of the adaptation to the level of the transmitting transistors used in the LUT and the original encoding of conjunctions in disjunctive normal form. The programming of one variable for the proposed structure of DNF-LUT is considered. There is drawn a conclusion about the advisability of applying advanced methods for the implementation of systems of logic functions in programmable logic integrated circuits of the field programmable gate array type.

$\textbf{Keywords:} \ \ \text{Field programmable gate array, Look-Up Table, System of logical functions, , DC-LUT, DNF-LUT.}$

Введение. В настоящее время для реализации цифровых элементов и устройств вычислительной техники, а также систем управления широко используются программируемые логические интегральные схемы (ПЛИС). Большинство ПЛИС типа FPGA (Field-programmable gate array) основано на так называемых Look-Up Tables (LUTs), или таблицах истинности [1–7]. Однако существующие LUTs реализуют только одну логическую функцию, заданную в СДНФ, и не ориентированы на системную реализацию, так как для реализации систем из *т* функций потребуется *т* логических элементов, что, в свою очередь, ведет к значительным аппаратным затратам. В связи с этим предлагаются усовершенствованные методы реализации систем логических функций в СДНФ, а также в ДНФ, которые позволят получить существенный выигрыш в аппаратных затратах.

Усовершенствованный метод реализации в FPGA систем логических функций, заданных в СДНФ. Как было изложено, логические элементы (ЛЭ) ПЛИС типа FPGA базируются на LUTs, которые реализованы на мультиплексоре, представляющем из себя дерево передающих транзисторов [16]. Подавая на входы данных настраивающие константы, мы можем реализовать любые логические функции.

Логическая функция, которую реализует простейший 1-LUT, выглядит следующим образом:

$$z_{out} = d_0 \cdot \overline{x} \vee d_1 \cdot x. \tag{1}$$

В дереве передающих транзисторов, реализующих (1), в зависимости от сигнала x на входе инвертора функции сигналы всегда ортогональны, т.е. со входов настройки всегда подаётся либо 0, либо 1, и нет ситуации, когда оба передающих транзистора по x и не x не активированы.

Ранее предлагалось выполнить реверс (1) для дешифрации входного набора с обеспечением ортогональности по каждой переменной в каждой ветви дерева [8]:

$$d_{out.i} = & (x_j^{\sigma(i-1,j)} \lor x_j^{\sigma(i-1,j)}); i = 1, 2^n.$$

(2)

Для программирования значений m логических функций предлагается:

$$z_{l} = \bigvee_{i=1}^{N} (d_{out.i} \cdot h_{l.i}); l = 1, m,$$

(3)

где h — настройка вхождения конституент i в данную функцию из m функций системы.

Элементарный DC LUT на одну переменную (1- DC LUT) получается путём передачи сигнала в элементарном 1- LUT в другом направлении [9–16], получаем дешифратор (DC).

Логическая функция, которую реализует DC LUT, можно записать следующим образом:

$$\overline{d}_{out,0}(x) = \overline{x}; \ \overline{d}_{out,1}(x) = x.$$

(4)

Усовершенствованный метод реализации в FPGA систем логических функций, заданных в ДНФ. Для реализации функций большого числа переменных предлагается программирование не в СДНФ, а в ДНФ.

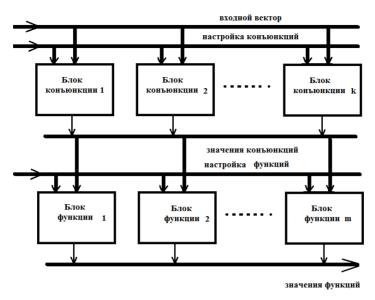

Предлагаемый новый ДНФ-LUT представляет собой конфигурируемую пользователем структуру, аналогичную программируемой логической матрице ПЛМ, для программирования которой необходим специальный программатор [17–23]. Конфигурирование ДНФ-LUT предполагается таким же, как и в обычном LUT, путём загрузки оперативной памяти ОЗУ (SRAM). На рис. 1 представлена структура ДНФ-LUT.

Таким образом, вместо загрузки значений таблицы истинности программируются лишь значения конъюнкций длиной n, где n — число переменных m логических функций. Вхождение k конъюнкций в m функций также программируется настройкой функций. По заданному входному набору (вектору) n переменных блоки конъюнкций вычисляют значения k конъюнкций, которые далее формируют «по ИЛИ» значения m логических функций.

Рис. 1. Логический элемент ДНФ-LUT

Рассмотрим программирование одной i-й переменной. Предлагается выражение:

$$s_{i} = (d_{SRAM.i} \cdot d_{in} \vee \overline{d}_{SRAM.i} \cdot d_{0}) \cdot x_{i} \vee \vee (d_{SRAM.\overline{i}} \cdot d_{in} \vee \overline{d}_{SRAM.\overline{i}} \cdot d_{0}) \cdot \overline{x}_{i}; i = n.$$

(5)

В выражении (9)  $d_{SRAM.i}$ ,  $d_{SRAM.i}$ , — настройка вхождения i-й переменной из n переменных в j-ю конъюнкцию системы из m функций;  $d_{in}$  — входная константа, которая должна формироваться при «правильном» значении переменной либо её несущественности;  $d_0$  — признак того, что заданная переменная имеет «неправильное» значение. Этот признак передаётся дальше, он участвует в формировании значения конъюнкции.

Суть в том, что в случае несущественности переменной значение выражения (5) было эквивалентно значению выражения при правильном заданном значении переменной, т.е. если  $d_{SRAM.i}=1; d_{SRAM.i}=0$ , переменная существенна и должна быть равна 1 (без инверсии), при  $d_{SRAM.i}=0; d_{SRAM.i}=1$  переменная существенна и должна быть равна 0 (с инверсией), при  $d_{SRAM.i}=1; d_{SRAM.i}=1$  переменная не существенна.

Значения  $d_{SRAM.i} = 0$ ;  $\bar{d}_{SRAM.i} = 0$  запрещены. Рассмотрим пример. Пусть i-я переменная должна быть 1. Настройка для этого случая приведена в табл. 1.

Таблица 1 Задание значения 1 для *i-*й переменной

| $d_{SRAM.i}$ | $d_{_{SRAMi}}$ | $d_{in}$ | $d_0$ | X <sub>i</sub> | –<br>Xi | S <sub>i</sub> |

|--------------|----------------|----------|-------|----------------|---------|----------------|

| 1            | 0              | 1        | 0     | 1              | 0       | 1              |

| 1            | 0              | 1        | 0     | 0              | 1       | 0              |

Рассмотрим подробно. Пусть заданная переменная равна 1:

$$\begin{aligned} \mathbf{s}_{i=1} &= [(\mathbf{d}_{SRAM.i} = 1) \cdot (\mathbf{d}_{in} = 1) \cdot (\bar{\mathbf{d}}_{SRAM.i} = 0) \cdot (\mathbf{d}_{0} = 0))] \cdot (\mathbf{x}_{i} = 1) \vee \\ &\vee [(\mathbf{d}_{SRAM.\bar{i}} = 0) \cdot (\mathbf{d}_{in} = 1) \vee (\bar{\mathbf{d}}_{SRAM.\bar{i}} = 1) \cdot (\mathbf{d}_{0} = 0))] \cdot (\bar{\mathbf{x}}_{i} = 0) = 1. \end{aligned} \tag{6}$$

Пусть заданная переменная равна 0:

$$\begin{split} s_{i=0} &= [(d_{SRAM.i} = 1) \cdot (d_{in} = 1) \cdot (\bar{d}_{SRAM.i} = 0) \cdot (d_{0} = 0))] \cdot (x_{i} = 0) \cdot \\ &\vee [(d_{SRAM.\bar{i}} = 0) \cdot (d_{in} = 1) \cdot (\bar{d}_{SRAM.\bar{i}} = 1) \cdot (d_{0} = 0))] \cdot (\bar{x}_{i} = 1) = 0. \end{split} \tag{7}$$

Пусть i-я переменная должна быть 0. Настройка для этого случая приведена в табл. 2:

Таблица 2 Задание значения 0 для i-й переменной

|   | $\boldsymbol{d}_{\text{SRAM.i}}$ | $d_{_{SRAMar{i}}}$ | $d_{in}$ | $d_0$ | X <sub>i</sub> | –<br>Xi | Si |

|---|----------------------------------|--------------------|----------|-------|----------------|---------|----|

| ſ | 0                                | 1                  | 1        | 0     | 0              | 1       | 1  |

|   | 0                                | 1                  | 1        | 0     | 1              | 0       | 0  |

Рассмотрим подробно. Пусть заданная переменная равна 0:

$$\begin{aligned} s_{i=1} &= [(d_{SRAM.i} = 0) \cdot (d_{in} = 1) \vee (\overline{d}_{SRAM.i} = 1) \cdot (d_{0} = 0))] \cdot (x_{i} = 0) \vee \\ &\vee [(d_{SRAM.\bar{i}} = 1) \cdot (d_{in} = 1) \vee (\overline{d}_{SRAM.\bar{i}} = 0) \cdot (d_{0} = 0))] \cdot (\overline{x_{i}} = 1) = 1. \end{aligned} \tag{8}$$

Пусть заданная переменная равна 1:

$$s_{i=0} = [(d_{SRAM.i} = 0) \cdot (d_{in} = 1) \vee (\overline{d}_{SRAM.i} = 1) \cdot (d_{0} = 0))] \cdot (x_{i} = 1) \vee (\overline{d}_{SRAM.i} = 1) \cdot (d_{0} = 0))] \cdot (x_{i} = 1) \vee (\overline{d}_{SRAM.i} = 0) \cdot (d_{0} = 0))] \cdot (\overline{x}_{i} = 0) = 0.$$

(9)

Если заданная переменная несущественна (табл. 3).

Таблица 3 3адание несущественной i-й переменной

| d <sub>SRAM.i</sub> | d <sub>SRAMi</sub> | $d_{in}$ | $d_0$ | X <sub>i</sub> | –<br>Xi | Si |

|---------------------|--------------------|----------|-------|----------------|---------|----|

| 1                   | 1                  | 1        | 0     | 1              | 0       | 1  |

| 1                   | 1                  | 1        | 0     | 0              | 1       | 1  |

Пусть заданная несущественная переменная равна 1:

$$s_{i=1} = [(d_{SRAM.i} = 1) \cdot (d_{in} = 1) \vee (\bar{d}_{SRAM.i} = 1) \cdot (d_{0} = 1))] \cdot (x_{i} = 1) \vee \\ \vee [(d_{SRAM.i} = 1) \cdot (d_{in} = 1) \vee (\bar{d}_{SRAM.i} = 1) \cdot (d_{0} = 0))] \cdot (\bar{x}_{i} = 0) = 1$$

(10)

Пусть заданная несущественная переменная равна 0:

$$\begin{aligned} \mathbf{s}_{i=0} &= [(\mathbf{d}_{SRAM.i} = 1) \cdot (\mathbf{d}_{in} = 1) \vee (\bar{\mathbf{d}}_{SRAM.i} = 1) \cdot (\mathbf{d}_{0} = 1))] \cdot (\mathbf{x}_{i} = 0) \vee \\ &\vee [(\mathbf{d}_{SRAM.\bar{i}} = 1) \cdot (\mathbf{d}_{in} = 1) \vee (\bar{\mathbf{d}}_{SRAM.\bar{i}} = 1) \cdot (\mathbf{d}_{0} = 0))] \cdot (\bar{\mathbf{x}}_{i} = 1) = 1 \end{aligned} \tag{11}$$

Выражения (5) для всех переменных данной конъюнкции могут быть объединены последовательно:

$$\overset{n}{\underset{i=1}{\&}} \{ (d_{SRAM.i} \cdot d_{in} \vee \overline{d}_{SRAM.i} \cdot d_{0}) \cdot x_{i} \vee (d_{SRAM.\overline{i}} \cdot d_{in} \vee \overline{d}_{SRAM.\overline{i}} \cdot d_{in}) \times \overline{d}_{SRAM.\overline{i}} \cdot d_{0} \cdot \overline{x}_{i} \}.$$

(12)

Причём  $d_{in} = 1$  (5) для старшей переменной и передаёт логическую единицу, которая транслируется на выход всей цепочки.

При параллельной реализации для всей заданной конъюнкции:

$$\begin{array}{l}

\stackrel{n}{\underset{i=1}{\vee}} \{ (d_{SRAM.i} \cdot d_{in} \vee \overline{d}_{SRAM.i} \cdot d_{0}) \cdot x_{i} \vee (d_{SRAM.\overline{i}} \cdot d_{in} \vee \overline{d}_{SRAM.\overline{i}} \cdot d_{in} \vee \overline{d}_{SRAM.\overline{i}} \cdot d_{0}) \cdot \overline{x}_{i} \}.

\end{array}$$

(13)

В первом случае (6) конъюнкция «набирается», т.е. активируется соответствующая цепочка, если все переменные «правильные» – либо несущественны, либо равны заданному значению, т.е. значение сигнала на её выходе равно логической единице.

Если хотя бы одна переменная «неправильная», цепочка не активируется, т.е. значение сигнала на её выходе равно логическому нулю. Разрыв цепочки недопустим. Во втором случае конъюнкция не активируется, если хотя бы она параллельная цепочка «неправильная».

Выражения (8) или (9) описывают условия активирования соответствующей j-й конъюнкции системы из m функций.

Для программирования значений m логических функций в ДНФ-LUT:

$$z_1 = \bigvee_{i=1}^{k} (d_j \cdot h_{l,j}); l = 1, m.$$

(14)

Таким образом, конфигурирование осуществляется не по  $2^n$  наборам функций n переменных, а более компактно в случае, если количество конъюнкций в системе функций гораздо меньше  $2^n$ .

**Выводы.** Модификация метода реализации систем логических функций в ДНФ на базе ПЛМ заключается в том, что выполнена адаптация к уровню передающих транзисторов, используемых в LUT, и применено оригинальное кодирование конъюнкций ДНФ, обеспечивающее формирование значения конъюнкции. Предлагаемое техническое решение ДНФ-LUT защищено патентом РФ. Целесообразно выполнить моделирование и получить оценки сложности для последующей оптимизации.

#### Библиографический список

- 1. Тюрин С.Ф. О реализации логических функций шести переменных в адаптивном логическом модуле FPGA STRATIX III // Вестник Пермского национального исследовательского политехнического университета. Электротехника, информационные технологии, системы управления. -2016. -№ 19. -C. 41–54.

- 2. Тюрин С.Ф. Дерево транзисторов для реализации систем логических функций // Вестник Пермского национального исследовательского политехнического университета. Электротехника, информационные технологии, системы управления. 2015. № 2(14). С. 37–45.

- 3. Тюрин С.Ф. Повышение достоверности функционирования логических элементов LUT FPGA // Вестник Пермского национального исследовательского политехнического университета. Электротехника, информационные технологии, системы управления. 2014. N 3(11). С. 5–33.

- 4. Угрюмов Е.П. Цифровая схемотехника: учеб. пособие. СПб.: БХВ-Петербург, 2004. 518 с.

- 5. Строгонов А., Цыбин С. Программируемая коммутация ПЛИС: взгляд изнутри [Электронный ресурс]. URL: http://www.kit-e.ru/articles/plis/2010\_11\_56.php (дата обращения: 16.12.2014).

- 6. Золотуха Р., Комолов Д. Stratix III новое семейство FPGA фирмы Altera [Электронный ресурс]. URL: http://kite.ru/assets/files/pdf/2006\_12\_30.pdf (дата обращения: 28.11.2015).

- 7. Использование ресурсов ПЛИС Stratix III фирмы Altera при проектировании микропроцессорных ядер [Электронный ресурс]. URL: file:///C:/Users/%D0%A2%D1%8E%D1%80%D0%B8%D0%BD/Desktop/%D0%A6%D1%8B%D0%B1%D0%B8%D0%BD%2010%20%D0%B3%D0%BE%D0%B4.pdf (дата обращения: 27.11.2015).

- 8. Тюрин С.Ф., Вихорев Р.В. Усовершенствованный метод реализации в FPGA систем логических функций, заданных в СДНФ [Электронный ресурс] // Инженерный вестник Дона. 2017. № 1. URL: ivdon.ru/ru/magazine/archive/n1y2017/4044 (дата обращения: 27.11.2015).

- 9. Пат. 2573732 Рос. Федерация: МПК G06F 7/57 H03K 19/173. Программируемое логическое устройство / заяв. и патентообл. С.Ф. Тюрин, Р.В. Вихорев. № 2014107336/08, заявл. 25.02.2014; опубл. 27.01.2016. Бюл. № 3.

- 10. Пат. 2602780 Рос. Федерация: МПК G06F 7/57 H03K 19/173. Программируемое логическое устройство / заяв. и патентообл. С.Ф. Тюрин, Р.В. Вихорев, А.Ю. Плотникова. № 2014115537/08, заявл. 17.04.2014; опубл. 20.11.2016. Бюл. № 32.

- 11. Пат. 2547229 Рос. Федерация: МПК G06F 7/57 H03K 19/173. Программируемое логическое устройство / заяв. и патентообл. С.Ф. Тюрин, А.Ю. Городилов, Р.В. Вихорев. № 2014120558/08, заявл. 21.05.2014; опубл. 10.04.2015. Бюл. № 10.

- 12. Тюрин С.Ф., Прохоров А.С. Усовершенствованный логический элемент FPGA [Электронный ресурс] // Вестник Воронеж. гос. ун-та. Сер. Системный анализ и информационные технологии. 2016. № 4. URL: vestnik.vsu.ru/pdf/analiz/2016/04/2016-04-12.pdf (дата обращения: 27.01.2017).

- 13. Тюрин С.Ф., Городилов А.Ю., Данилова Е.Ю. Диагностирование логического элемента DC LUT FPGA [Электронный ресурс] // Инженерный вестник Дона. -2016. -№ 1. URL: ivdon.ru/ru/magazine/archive/n2y2014/2313 (дата обращения: 27.01.2017).

- 14. Тюрин С.Ф., Прохоров А.С. Логический элемент FPGA, вычисляющий две функции одновременно // Проектирование и технология электронных средств. -2016. -№ 2. -C. 18–23.

- 15. Тюрин С.Ф. Функционально-полные толерантные элементы ПЛИС FPGA для аэрокосмических вычислительных комплексов // Вестник Сибир. гос. аэрокосм. ун-та им. акад. М.Ф. Решетнева. 2016. N 2. С. 484—489.

- 16. FPGA Architecture [Электронный ресурс]. URL: altera.com/en\_US/pdfs/literature/wp/wp-01003.pdf (дата обращения: 27.01.2017).

- 17. Vikhorev R. Universal logic cells to implement systems functions // Proceedings of the 2016 IEEE North West Russia Section Young Researchers in Electrical and Electronic Engineering Conference, EIConRusNW 2016. 2016. C. 373–375.

- 18. Тюрин С.Ф., Городилов А.Ю., Вихорев Р.В. Модифицированный логический элемент LUT FPGA // Вестник Перм. ун-та. Сер. Математика. Механика. Информатика. 2014. № 1(24). С. 69–74.

- 19. Тюрин С.Ф., Плотникова А.Ю., Вихорев Р.В. Анализ надёжности логических элементов с избыточным базисом при учёте резервирования входов // Вестник Перм. ун-та. Сер. Математика. Механика. Информатика. 2014. N 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014. 2014.

- 20. Вихорев Р.В., Зажигин Ю.Е. Обзор методов тестирования и диагностики FPGA // Актуальные вопросы образования и науки: сб. науч. тр. по материалам междунар. науч.-практ. конф.: в 14 ч. Ч. 9. Тамбов: Изд-во ТРОО «Бизнес-Наука-Общество» 2014. С. 44–47.

- 21. Тельпухов Д.В., Рухлов В.С., Рухлов И.С. Исследование и разработка методов оценки сбоеустойчивости комбинационных схем, реализованных в базисе ПЛИС [Электронный ресурс] // Инженерный вестник Дона. 2016. № 1. URL: ivdon.ru/ru/magazine/archive/n1y2016/3504 (дата обращения: 27.02.2017).

- 22. Logic Array Blocks and Adaptive Logic Modules in Stratix III Devices [Электронный ресурс]. URL: altera.com.cn/content/dam/altera\_www/global/zh\_CN/pdfs/literature/hb/stx3/ stx3\_siii51002.pdf (дата обращения: 27.02.2017).

- 23. Пат. 2544750 Рос. Федерация: МПК G06F 7/57 H03K 19/173. Программируемое логическое устройство / заяв. и патентообл. С.Ф. Тюрин. № 2014120774/08 22.05.2014 опубл. 20.03.2015. Бюл. № 8.

#### References

- 1. Tiurin S.F. O realizatsii logicheskikh funktsii shesti peremennykh v adaptivnom logicheskom module FPGA STRATIX III [About realization of Logical functions of six variables in the adaptive logic module FPGA STRATIX III]. Vestnik Permskogo natsional'nogo issledovatel'skogo politekhnicheskogo universiteta. Elektrotekhnika, informatsionnye tekhnologii, sistemy upravleniia, 2016, no. 19, pp. 41-54.

- 2. Tiurin S.F. Derevo tranzistorov dlia realizatsii sistem logicheskikh funktsii [The tree of transistors is for the realization of systems of logic functions]. *Vestnik Permskogo natsional'nogo issledovatel'skogo politekhnicheskogo universiteta. Elektrotekhnika, informatsionnye tekhnologii, sistemy upravleniia*, 2015, no. 2(14), pp. 37-45.

- 3. Tiurin S.F. Povyshenie dostovernosti funktsionirovaniia logicheskikh elementov LUT FPGA [Increase of reliability of functioning of elements LUT FPGA]. Vestnik Permskogo natsional'nogo issledovateľ skogo politekhnicheskogo universiteta. Elektrotekhnika. informatsionnye tekhnologii, sistemy upravleniia, 2014, no. 3(11), pp. 5-33.

- 4. Ugriumov E.P. Tsifrovaia skhemotekhnika [Digital circuitry]. Saint Petersburg: BKhV-Peterburg, 2004. 518 p.

- 5. Strogonov A., Tsybin S. Programmiruemaia kommutatsiia PLIS: vzgliad iznutri [Programmable switching of FPGA: inside view], available at: http://www.kit-e.ru/articles/plis/2010\_11\_56.php (accessed 16 December 2014).

- 6. Zolotukha R., Komolov D. Stratix III novoe semeistvo FPGA firmy Altera [Stratix III a new FPGA family of Altera], available at: http://kite.ru/assets/files/pdf/2006\_12\_30.pdf (accessed 28 November 2015).

- 7. Ispol'zovanie resursov PLIS Stratix III firmy Altera pri proektirovanii mikroprotsessornykh iader [Using of Stratix III FPGA of Altera's resources], available at: file:///C:/Users/%D0%A2%D1%8E%D1%80%D0%B8%D0%BD/Desktop/%D0%A6%D1%8B%D0%B1%D0%B8%D0%B8%D0%BD%2010%20%D0%B3%D0%BE%D0%B4.pdf (accessed 27 November 2015).

- 8. Tiurin S.F., Vikhorev R.V. Usovershenstvovannyi metod realizatsii v FPGA sistem logicheskikh funktsii, zadannykh v SDNF [An improved method for implementing in FPGA systems of logical functions specified in

- the PDNF]. *Inzhenernyi vestnik Dona*, 2017, no. 1, available at: ivdon.ru/ru/magazine/archive/n1y2017/4044 (accessed 27 November 2015).

- 9. Tiurin S.F., Vikhorev R.V. Programmiruemoe logicheskoe ustroistvo [Programmable logic unit]. Patent Rossiiskaia Federatsiia no. 2573732 (2016).

- 10. Tiurin S.F., Vikhorev R.V., Plotnikova A.Iu. Programmiruemoe logicheskoe ustroistvo [Programmable logic unit]. Patent Rossiiskaia Federatsiia no. 2602780 (2016).

- 11. Tiurin S.F., Gorodilov A.Iu., Vikhorev R.V. Programmiruemoe logicheskoe ustroistvo [Programmable logic unit]. Patent Rossiiskaia Federatsiia no. 2547229 (2015).

- 12. Tiurin S.F., Prokhorov A.S. Usovershenstvovannyi logicheskii element FPGA [An improved logic element of FPGA]. *Vestnik Voronezhskogo gosudarstvennogo universiteta. Sistemnyi analiz i informatsionnye tekhnologii*, 2016, no 4, available at: vestnik.vsu.ru/pdf/analiz/2016/04/2016-04-12.pdf (accessed 27 January 2017).

- 13. Tiurin S.F., Gorodilov A.Iu., Danilova E.Iu. Diagnostirovanie logicheskogo elementa DC LUT FPGA [Diagnostics of a logic element of DC LUT FPGA]. *Inzhenernyi vestnik Dona*, 2016, no. 1, available at: ivdon.ru/ru/magazine/archive/n2y2014/2313 (accessed 27 January 2017).

- 14. Tiurin S.F., Prokhorov A.S. Logicheskii element FPGA, vychisliaiushchii dve funktsii odnovremenno [The FPGA logic element, which computes two functions simultaneously]. *Proektirovanie i tekhnologiia elektronnykh sredstv*, 2016, no. 2, pp. 18-23.

- 15. Tiurin S.F. Funktsional'no-polnye tolerantnye elementy PLIS FPGA dlia aerokosmicheskikh vychislitel'nykh kompleksov [Functional-completed tolerant FPGA elements for aerospace computing systems]. *Vestnik Sibirskogo gosudarstvennogo aerokosmicheskogo universiteta imeni akademika M.F. Reshetneva*, 2016, no. 2, pp. 484-489.

- 16. FPGA Architecture, available at: altera.com/en\_US/pdfs/literature/wp/wp-01003.pdf (accessed 27 January 2017).

- 17. Vikhorev R. Universal logic cells to implement systems functions. *Proceedings of the 2016 IEEE North West Russia Section Young Researchers in Electrical and Electronic Engineering Conference, EIConRusNW 2016*, 2016, pp. 373-375.

- 18. Tiurin S.F., Gorodilov A.Iu., Vikhorev R.V. Modifitsirovannyi logicheskii element LUT FPGA [Modified logic element LUT FPGA]. *Vestnik Permskogo unversiteta. Matematika. Mekhanika. Informatika*, 2014, no. 1(24), pp. 69-74.

- 19. Tiurin S.F., Plotnikova A.Iu., Vikhorev R.V. Analiz nadezhnosti logicheskikh elementov s izbytochnym bazisom pri uchete rezervirovaniia vkhodov [Analysis of the reliability of logical elements with a redundant basis considering the reservation of inputs]. *Vestnik Permskogo unversiteta*. *Matematika*. *Mekhanika*. *Informatika*, 2014, no. 4(27), pp. 104-110.

- 20. Vikhorev R.V., Zazhigin Iu.E. Obzor metodov testirovaniia i diagnostiki FPGA [Review of FPGA testing and diagnostic methods]. Chornik nauchnykh trudov po materialam mezhdunarodnoi nauchnoprakticheskoi konferentsii "Aktual'nye voprosy obrazovaniia i nauki". Part 9. Tambov: TROO "Biznes-Nauka-Obshchestvo", 2014, pp. 44-47.

- 21. Tel'pukhov D.V., Rukhlov V.S., Rukhlov I.S. Issledovanie i razrabotka metodov otsenki sboeustoichivosti kombinatsionnykh skhem, realizovannykh v bazise PLIS [Research and development of methods for estimating the fault tolerance of combinational circuits implemented in the basis of FPGAs]. *Inzhenernyi vestnik Dona*, 2016, no. 1, available at: ivdon.ru/ru/magazine/archive/n1y2016/3504 (accessed 27 February 2017).

- 22. Logic Array Blocks and Adaptive Logic Modules in Stratix III Devices, available at: altera.com.cn/content/dam/altera\_www/global/zh\_CN/pdfs/literature/hb/stx3/ stx3\_siii51002.pdf (accessed 27 February 2017).

- 23. Tiurin S.F. Programmiruemoe logicheskoe ustroistvo [Programmable logic unit]. Patent Rossiiskaia Federatsiia no. 2544750 (2015).

## Сведения об авторах

Вихорев Руслан Владимирович (Пермь, Россия) — инженерконструктор ПАО «Пермская научно-производственная приборостроительная компания», аспирант кафедры автоматики и телемеханики Пермского национального исследовательского политехнического университета (614990, Пермь, Комсомольский пр., 29, e-mail: vihrusvla@gmail.com).

**Тюрин Сергей Феофентович** (Пермь, Россия) – заслуженный изобретатель Российской Федерации, доктор технических наук, профессор кафедры автоматики и телемеханики Пермского национального исследовательского политехнического университета (614990, Пермь, Комсомольский пр., 29, e-mail: tyurinsergfeo@yandex.ru).

#### About the authors

Vikhorev Ruslan Vladimirovich (Perm, Russian Federation) is a design engineer Public Joint-stock "Perm Scientific Industrial Instrument-Making Company", postgraduate student at the Department of Automation and Telemechanics Perm National Research Polytechnic University (614990, Perm, 29, Komsomolsky pr., e-mail: vihrusvla@gmail.com).

**Tyurin Sergey Feofentovich** (Perm, Russian Federation) is a Honored Inventor of the Russian Federation, Doctor of Technical Sciences, Professor at the Department of Automation and Telemechanics Perm National Research Polytechnic University (614990, Perm, 29, Komsomolsky pr., e-mail: tyurinsergfeo@yandex.ru).

Получено 31.07.2017