2014 Электротехника, информационные технологии, системы управления

No 12

УДК 681.3

## С.Ф. Тюрин

Пермский национальный исследовательский политехнический университет, Пермь, Россия

# РАДИАЦИОННО-УСТОЙЧИВАЯ ЯЧЕЙКА SRAM

Анализируется радиационно-устойчивая ячейка памяти DICE – SRAM. Показывается, что она представляет собой дублированный SR-триггер с инверсными входами – автомат Мура. Выводятся характеристические уравнения, описывающие DICE – SRAM. Проводится моделирование в системе схемотехнического моделирования NI Multisim 10 фирмы National Instruments Electronics Workbench Group и устанавливаются виды отказов, парируемых ячейкой. Предлагается отказо- и сбоеустойчивая ячейка памяти SRAM с учетверением транзисторов QSRAM. Показывается предпочтительность такого технического решения по ряду показателей – в сравнении с троированием – известным вариантом TMR (Triple Modular Redundancy).

**Ключевые слова:** радиационно-устойчивая ячейка памяти DICE – SRAM, характеристические уравнения, сбои, отказы, система схемотехнического моделирования NI Multisim, SRAM с учетверением транзисторов – QSRAM, троирование –TMR (Triple Modular Redundancy).

## S.F. Tyurin

Perm National Research Polytechnic University, Perm, Russian Federation

### SIMULATION OF THE RADIATION-STEADY DICE SRAM CELL

In the work are obtained the equations, which describe the radiation- steady DICE SRAM cell. Is described the simulation of the DICE SRAM cell by NI Multisim system.

**Keywords**: SRAM cell, DICE SRAM cell, failure, quadrupling SRAM cell, QSRAM cell, failure, NI Multisim.

Введение. В настоящее время активно развивается направление создания радиационно-стойких микросхем для космических, специальных и военных применений. Лидером является компания Atmel [1]. При воздействии заряженных частиц на КМОП-транзисторы могут происходить скачки напряжения питания, что приводит к сбоям переключений транзисторов – SET (Single Event Transient), защелкиваниям (Latch\_up), повреждениям шин питания. Это может привести к разрушениям транзисторов [2]. При попадании тяжелых заряженных частиц внутрь микросхемы могут возникать так называемые случайные воздействия – SEE (Single Event Effect), такие как, например, SEU (Single Event Upset) – сбои, изменяющие состояние логических элементов [2].

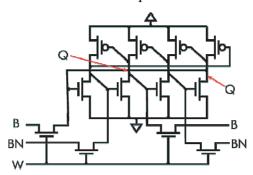

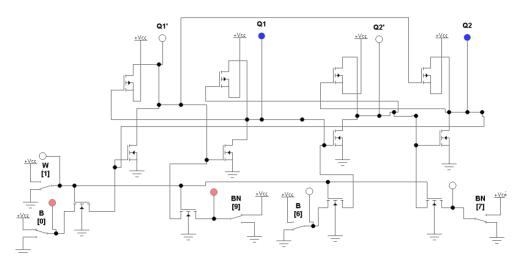

В ячейках памяти для парирования SEU используют особое дублирование — DICE (Dual Inter\_locked Storage). На рис. 1 изображено DICE-представление ячейки статической оперативной памяти SRAM [1, 2].

Рис. 1. DICE-реализация ячейки SRAM

Однако детальное описание таких ячеек в рассмотренных источниках отсутствует. Целесообразно изучить и выяснить особенности построения указанных устройств, выполнить их моделирование с методической целью, а также с целью рассмотрения возможностей дальнейшего их совершенствования в русле создания высоконадежной радиационно-стойкой аппаратуры.

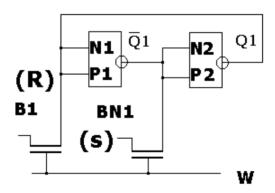

# **1.** Структура радиационно-стойкой ячейки DICE – SRAM. Представим инверторы триггера рис. 1 следующим образом:

Рис. 2. Структура ячейки SRAM при «разнесении» входов транзисторов n и p проводимостей одного транзистора

При «разнесении» входов транзисторов n и p проводимостей одного инвертора получим:

$$Q(t) = \overline{NP} = \overline{N \lor P}. \tag{1}$$

Для того чтобы выход инвертора стал равен логической 1, необходимо N=P=0, для того чтобы выход инвертора стал равен логическому 0, необходимо N=P=1.

Противоположные значения N и P запрещены, так как при N=1, P=0 оба транзистора T3, T4 закрыты и на выходе имеет место третье состояние (высокоимпедансное).

При N = 0, P = 1 оба транзистора открыты, что приводит к подключению шины питания на шину «0» вольт (Ground) — это короткое замыкание. Тогда получим с учетом монтажного И на входах:

$$Q_{1}(t+1) = \overline{(BN)_{1}} \overline{Q_{1}(t)B_{1} \vee Q_{1}(t)B_{1}} \vee (BN)_{1} \overline{Q_{1}(t)B_{1} \vee Q_{1}(t)B_{1}}.$$

(2)

Конечно, (2) упрощается до

$$Q_1(t+1) = \overline{(BN)_1 \overline{Q_1(t)B_1}}.$$

(3)

Радиационно-стойкую ячейку SRAM на основе дублирования триггеров, т.е. DICE – SRAM (рис. 1), представим следующим образом (рис. 3).

Рис. 3. Структура DICE – SRAM

На рис. З входы транзисторов N, P одного инвертора не объединены, управление каждым инвертором дублировано как бы по N и по P, с двух разных других инверторов, чтобы кратковременное изменение одного не привело к запоминанию неправильного значения. Каждый инвертор по своему выходу управляет двумя и управляется этими же двумя (таблица).

| Управление инверторами | DICE – | SRAM |

|------------------------|--------|------|

|------------------------|--------|------|

|   | 1 | 2 | 3 | 4 |

|---|---|---|---|---|

| 1 |   | 1 |   | 1 |

| 2 | 1 |   | 1 |   |

| 3 |   | 1 |   | 1 |

| 4 | 1 |   | 1 |   |

$$\begin{cases} Q_{1}'(t) = \overline{Q_{1}}\overline{B_{1}Q_{2}} = \overline{Q_{1}} \vee \overline{B_{1}Q_{2}}, \\ Q_{1}(t) = \overline{Q_{2}'(BN)_{1}Q_{1}'} = \overline{Q_{2}' \vee (BN_{1})Q_{1}'}, \\ Q_{2}'(t) = \overline{Q_{2}}\overline{B_{2}Q_{1}} = \overline{Q_{2}} \vee \overline{B_{2}Q_{1}}, \\ Q_{2}(t) = \overline{Q_{1}'(BN)_{2}Q_{2}'} = \overline{Q_{1}' \vee (BN_{2})Q_{2}'}. \end{cases}$$

$$(4)$$

Тогда DICE – SRAM, как дублированный триггер, описывается двумя функциями переходов:

$$Q_{1}(t+1) = \overline{(BN)_{1}} \overline{Q_{1}(t)B_{2} \vee Q_{2}(t)B_{1}} \vee (BN)_{2} \overline{Q_{1}(t)B_{2} \vee Q_{2}(t)B_{1}},$$

(5)

$$Q_{2}(t+1) = \overline{(BN)_{2} \overline{Q_{1}(t)B_{2} \vee Q_{2}(t)B_{1}} \vee (BN)_{1} \overline{Q_{1}(t)B_{2} \vee Q_{2}(t)B_{1}}}.$$

(6)

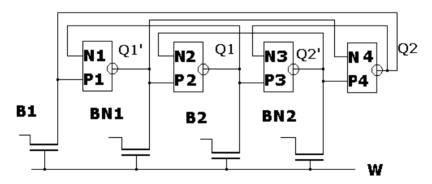

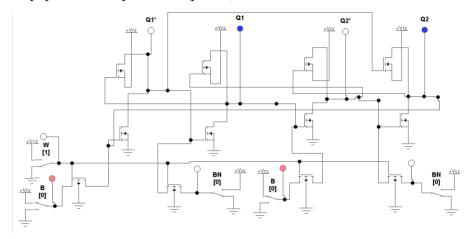

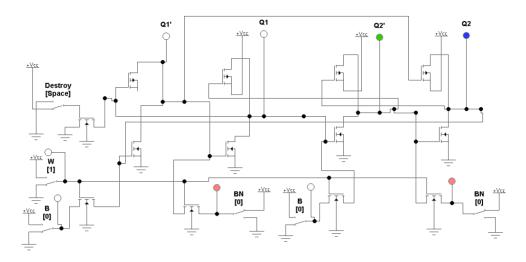

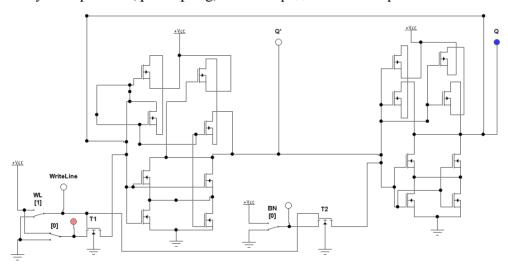

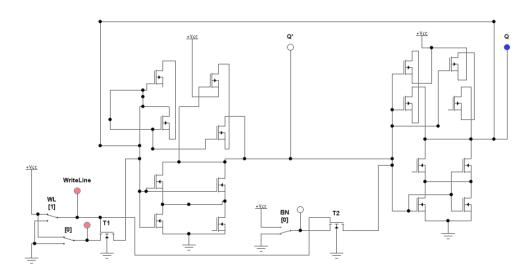

Моделирование радиационно-стойкой ячейки DICE – SRAM. Выполним моделирование радиационно-стойкой ячейки DICE – SRAM в системе схемотехнического моделирования NI Multisim 10 фирмы National Instruments Electronics Workbench Group [3, 7]. Запись 1 в радиационно-стойкую ячейку SRAM изображена на рис. 4.

Рис. 4. Запись 1 в радиационно-стойкую ячейку DICE – SRAM

На рис. 4 дублируются сигналы записи бита и его инверсия, оба триггера устанавливаются в состояние 1. После снятия сигнала записи W информация сохраняется (рис. 5).

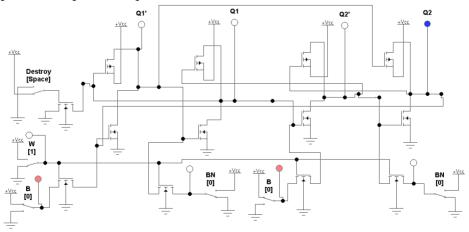

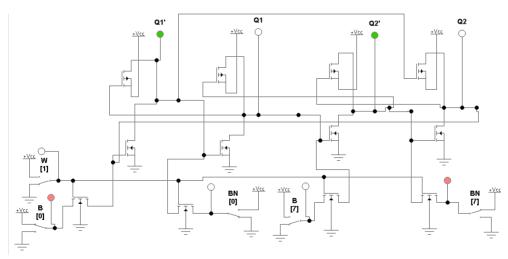

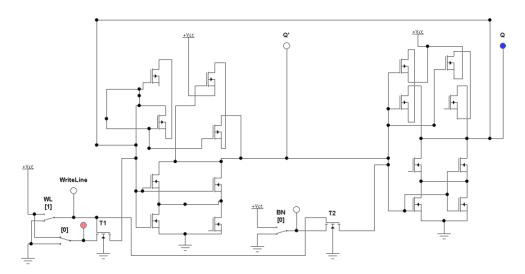

Рис. 5. Хранение 1 в радиационно-стойкой ячейке DICE – SRAM

Аналогично моделируются запись и хранение «нуля».

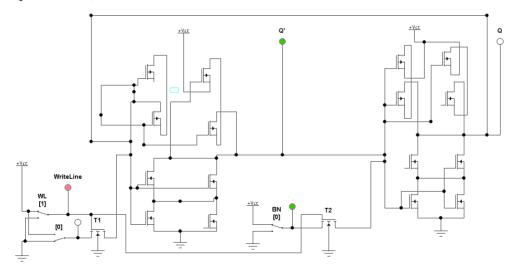

Моделирование сбоев и отказов в радиационно-стойкой ячейке DICE – SRAM. Выполним моделирование сбоя посредством формирования дестабилизирующего воздействия, например, на затвор транзистора N1 в том случае, когда в ячейке хранится 1 (рис. 6). Ключ Destroy с помощью дополнительного передающего транзистора подключает шину «ноль вольт» (Ground) (рис. 7). Видно, что выход Q1 неверный – не равен 1 при воздействии.

Рис. 6. Моделирование сбоя посредством формирования дестабилизирующего воздействия на затвор транзистора N1 при хранении 1

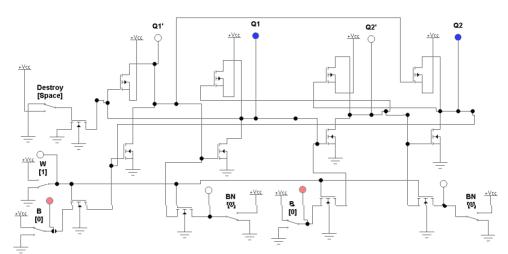

При снятии воздействия схема восстанавливается (Q1 = 1) (рис. 7).

Рис. 7. Восстанавление схемы после снятия воздействия

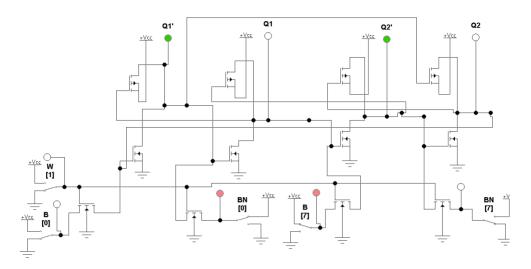

При хранении 0 (Q1 = 0) подобное воздействие не приводит к сбою (рис. 8).

Рис. 8. Моделирование сбоя посредством формирования дестабилизирующего воздействия на затвор транзистора N1 при хранении 0

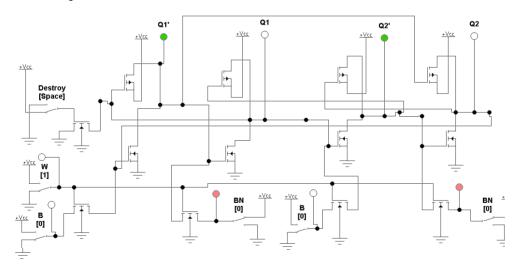

Выполним моделирование отказа, например, имитируем обрыв питания транзистора N1 (рис. 9).

Рис. 9. Моделирование отказа – обрыв питания транзистора N1. Ошибка

Таким образом, такой отказ приводит к ошибке! Рассмотрим ошибки при записи информации. Запись информации, как уже отмечалось, дублированная: если по разным каналам идут разные биты, то записывается единица (рис. 10, 11).

Рис. 10. Запись данных (по левому входу -1 (B[0]), по правому 0 (B[7]), записывается 1)

Рис. 11. Запись данных (по левому 0 (В[0]), по правому 1 (В[7]), записывается 1)

И это не хорошо, так как неизвестно, где правильный бит.

В случае если В равно BN, то правильная информация заносится (рис. 12).

Рис. 12. Запись данных (B = BN, заносится правильная информация)

A в случае если B[0] = BN[9] = 1, то B[6] = BN[7] = 0 (две ошибки), тоже неизвестно, где правильно (рис. 13).

Рис. 13. B[0] = BN[9] = 1, B[6] = BN[7] = 0 (две ошибки)

**Ячейка** – **QSRAM.** Предлагаемая QSRAM – отказосбоеустойчивая учетверенная (quadrupling) SRAM представлена на рис. 14.

Рис. 14. QSRAM – отказосбоеустойчивая учетверенная (quadrupling) SRAM

В QSRAM инверторы реализованы на элементе с избыточным базисом, так называемом функционально полном – толерантном элементе [3–6], реализующем функции:

$$x_1 x_2 \vee x_3 x_4,$$

(7)

$$(x_1 \vee x_2)(x_3 \vee x_4). \tag{8}$$

Следовательно, (7), (8) используются как:

$$\begin{array}{cccc} \overline{x} & \overline{x} & \sqrt{x} & \overline{x} \end{array}, \tag{9}$$

$$(\bar{x} \vee \bar{x})(\bar{x} \vee \bar{x}). \tag{10}$$

Сбой (ошибка) любого из четырех экземпляров переменной x не изменяет функций (9), (10).

С учетом того, что КМОП-структуры (7), (8) характеризуются наличием двух подсхем — подключения источника питания (z+) и двойственной ей схемы подключения шины «ноль вольт» (z-), получим выражения (11)–(14):

$$Z_{+FCT1} = \bar{x}_1 \bar{x}_2 \vee \bar{x}_3 \bar{x}_4, \tag{11}$$

$$Z_{-FCT1} = (x_1 \lor x_2)(x_3 \lor x_4), \tag{12}$$

$$Z_{+FCT2} = (\bar{x}_1 \vee \bar{x}_2)(\bar{x}_3 \vee \bar{x}_4), \tag{13}$$

$$Z_{-FCT2} = x_1 x_2 \vee x_3 x_4. \tag{14}$$

Таким образом, в каждом из инверторов (рис. 14) могут быть два сбоя (отказа) – в верхней и в нижней подсхемах.

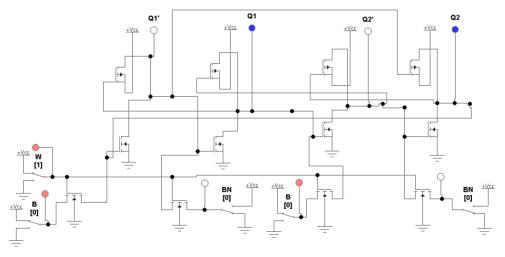

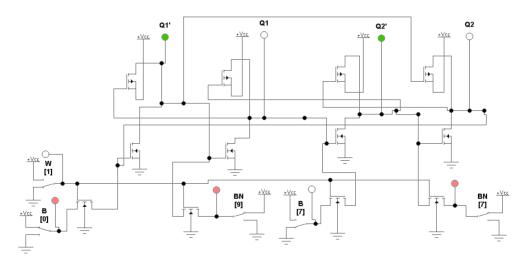

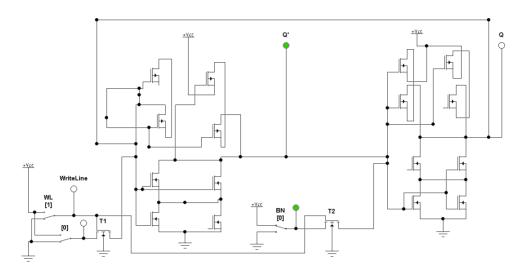

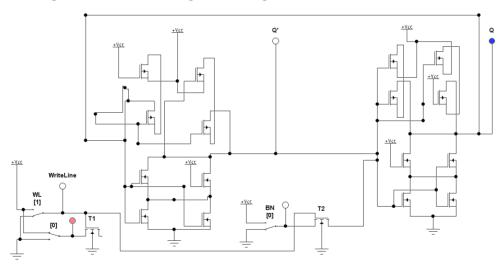

**Моделирование сбоев (отказов) в ячейке – QSRAM.** Выполним моделирование таких ситуаций, например, обрывов транзисторов (рис. 15–18).

Рис. 15. QSRAM-моделирование обрывов транзисторов в верхних и нижних подсхемах ФПТ-инверторов – запись 0

Рис. 16. QSRAM-моделирование обрывов транзисторов в верхних и нижних подсхемах ФПТ-инверторов – хранение 0

Рис. 17. QSRAM-моделирование обрывов транзисторов в верхних и нижних подсхемах  $\Phi\Pi T$ -инверторов – запись 1

Таким образом, схема работает правильно даже при отказах 4 транзисторов в ячейке QSRAM.

Рис. 18. QSRAM-моделирование обрывов транзисторов в верхних и нижних подсхемах ФПТ-инверторов – хранение 1

Единственным тонким местом остаются передающие транзисторы записи бита — T1, T2. Причем при обрыве одного, например T1, схема работает за счет второго — T2 (рис. 19).

Рис. 19. При обрыве Т1 схема работает за счет второго – Т2

В этом случае при сбое (отказе) одного из транзисторов в каждой «четверке» схема работает правильно. Возможно также для дальнейшего повышения надежности и учетверение линий передачи бита данных.

Сравнение ячейки QSRAM с троированными вариантами TMR SRAM. Сравним предлагаемую QSRAM с троированной ячейкой и мажоритарной схемой на выходе радиационно-стойкой ПЛИС фирмы Actel [1]. Зададим  $\lambda$  — интенсивность отказов (сбоев) транзисторов. Тогда для троированной схемы с одним мажоритарным элементом (мажоритаром)

$$P_{TT} = (3e^{-2\cdot12\lambda t} - 2e^{-3\cdot12\lambda t})e^{-14\lambda t},$$

(15)

где  $e^{-14\lambda t}$  – вероятность безотказной работы мажоритара.

Для QSRAM с учетом только отказов сбоев (отказов) одного транзистора (на самом деле парируется и некоторая часть отказов большего числа транзисторов) в каждой из двух подсхем каждого из двух ФПТ-элементов, работающих в режиме инвертора, получаем:

$$P(t)_{\text{OSRAM}} = \left[e^{-4\lambda_{m}t} + 4e^{-3\lambda_{m}t}(1 - e^{-\lambda_{m}t})\right]^{4} \left[e^{-4\lambda_{m}t} + 4e^{-3\lambda_{m}t}(1 - e^{-\lambda_{m}t})\right]^{2}.$$

(16)

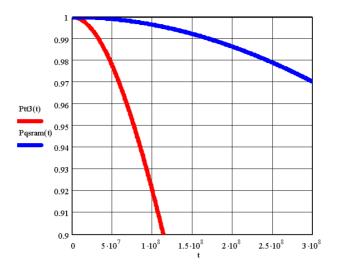

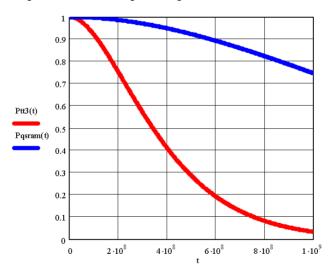

Сравнение вероятностей безотказной (бессбойной) работы троированной SRAM с мажоритарным элементом (Ptt) и QSRAM (Pqsram) показано на рис. 20.

Рис. 20. Сравнительный анализ вероятности безотказной работы троированного триггера с одним мажоритарным элементом (PTT) и QSRAM (PQSRAM)

Попробуем поставить три мажоритара для увеличения РТТ – РТТ3:

$$P_{tt3} = (3e^{-2\cdot12\cdot\lambda t} - 2e^{-3\cdot12\cdot\lambda t})(3e^{-2\cdot14\cdot\lambda t} - 2e^{-3\cdot14\cdot\lambda t}), \tag{17}$$

получим рис. 21.

Рис. 21. Сравнение вероятностей безотказной работы троированного триггера с тремя мажоритарными элементами (PTT3) и qsram (PQSRAM)

Следовательно, PQSRAM все равно выше PTT3, причем практически на всем временном интервале (рис. 22).

Рис. 22. Сравнение вероятностей безотказной работы троированного триггера с тремя мажоритарными элементами (PTT3) и qsram (PQSRAM) до вероятности 0,05

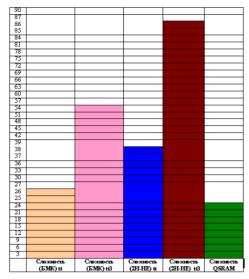

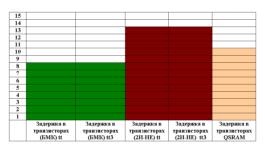

Результаты оценки вариантов построения отказоустойчивых ячеек SRAM по аппаратным затратам по количеству транзисторов и задержке представлены на рис. 23, 24.

Рис. 23. Сравнение сложности по числу транзисторов троированных вариантов SRAM и QSRAM

Рис. 24. Сравнение быстродействия по количеству транзисторов в наиболее «длинном» пути сигнала со входа на выход троированных вариантов SRAM и QSRAM

Заключение. Таким образом, анализ радиационно-стойкой ячейки DICE – SRAM как дублированного SR-триггера и автомата Мура позволил получить характеристические уравнения, показывающие возможность парирования сбоев, стремящихся изменить состояние одного из триггеров. За счет переменных, описывающих состояние другого триггера, «сбившийся» триггер восстанавливает правильное состояние.

Выполненное в системе NI Multisim 10 фирмы National Instruments Electronics Workbench Group схемотехническое моделирование двенадцатитранзисторной ячейки DICE – SRAM подтверждает факты парирования сбоев. С другой стороны, устанавливается фатальность отказов в одном из триггеров. Делается вывод о необходимости введения еще большей избыточности для парирования не только сбоев – SEU (Single Event Upset), но и отказов SEE (Single Event Effect).

Таким образом, предложенная ячейка статической оперативной памяти QSRAM с учетверением транзисторов парирует не только сбои – SEU (Single Event Upset), но и отказы SEE (Single Event Effect). QSRAM выигрывает у троированных вариантов SRAM как по сложности, так и по вероятности безотказной работы, незначительно проигрывая по задержке у варианта SRAM со специализированной реализацией мажоритаров (причем это практически заказная, «дорогая» реализация).

## Библиографический список

- 1. Цыбин С. Программируемая коммутация ПЛИС: взгляд изнутри [Электронный ресурс]. URL: http://www.kit-e.ru/articles/plis/2010\_11\_56.php (дата обращения: 02.09.2014).

- 2. Donald C. Mayer, Ronald C. Lacoe. Designing Integrated Circuits to Withstand Space Radiation [Электронный ресурс]. Vol. 4, № 2. Crosslink. URL: http://www.aero.org/publications/crosslink/summer2003/06.html (дата обращения: 20.09.2014).

- 3. Tyurin S.F. Retention of functional completeness of Boolean functions under «failures» of the arguments // Automation and Remote Control. 1999. 60 (9 PART 2). P. 1360–1367.

- 4. Тюрин С.Ф., Морозов А.Н. Отказоустойчивая ячейка памяти с использованием функционально-полных толерантных элементов // Вестник Пермского университета. Сер. Математика. Механика. Информатика. -2012. -№ 4. C. 68–75.

- 5. Тюрин С.Ф. Логические элементы с избыточным базисом // Вестник Пермского университета. Сер. Математика. Механика. Информатика. -2013. № 3(22). C. 91-105.

- 6. Тюрин С.Ф., Плотникова А.Ю. Концепция «зеленой» логики // Вестник Пермского национального исследовательского политехнического университета. Электротехника, информационные технологии, системы управления. 2013. № 58. C. 61-73.

- 7. NI Multisim [Электронный ресурс]. URL: http://sine.ni.com/np/app/main/p/docid/nav-98/lang/ru/ (дата обращения: 24.09.2014).

#### References

1. Tsybin S.A. Programmiruemaia kommutatsiia Programmíruemoi logícheskoi integrál'noi skhémy: vzgliad iznutri [Programmable switching of the Programmable logic integrated circuit: look from within]. Available at: http://www.kit-e.ru/articles/plis/ 2010\_11\_56.php (accessed: 02.09.2014).

- 2. Donald C. Mayer, Ronald C. Lacoe. Designing Integrated Circuits to Withstand Space Radiation. vol. 4, no. 2. Crosslink. Available at: http://www.aero.org/publications/crosslink/summer2003/06.html (accessed: 20.09.2014).

- 3. Tyurin S.F. Retention of functional completeness of Boolean functions under «failures» of the arguments. *Automation and Remote Control*, 1999, vol. 60, pp. 1360-1367.

- 4. Tiurin S.F., Morozov A.N. Otkazoustoichivaia iacheika pamiati s ispol'zovaniem funktsional'no-polnykh tolerantnykh elementov [Faulttolerant storage cell with use of functionally complete tolerant elements]. *Vestnik Permskogo universiteta. Matematika. Mekhanika. Informatika*, 2012, no. 4, pp. 68-75.

- 5. Tiurin S.F. Logicheskie elementy s izbytochnym bazisom [Logical elements with excess base]. *Vestnik Permskogo universiteta. Matematika. Mekhanika. Informatika*, 2013, no. 3(22), pp. 91-105.

- 6. Tiurin S.F., Plotnikova A.Iu. Kontseptsiia «zelenoi» logiki [Concept of "green" logic]. *Vestnik Permskogo natsional'nogo issledovatel'skogo politekhnicheskogo universiteta. Elektrotekhnika, informatsionnye tekhnologii, sistemy upravleniia*, 2013, no. 58, pp. 61-73.

- 7. NI Multisim. Available at: http://sine.ni.com/np/app/main/p/docid/nav-98/lang/ru/ (accessed: 24.09.2014).

## Сведения об авторе

**Тюрин Сергей Феофентович** (Пермь, Россия) — заслуженный изобретатель Российской Федерации, доктор технических наук, профессор кафедры автоматики и телемеханики Пермского национального исследовательского политехнического университета (614990, Пермь, Комсомольский пр., 29, e-mail: tyurinsergfeo@yandex.ru).

### About the author

**Tyurin Sergey Feofentovich** (Perm, Russian Federation) is Honored Inventor of the Russian Federation, Doctor of Technical Sciences, Professor at the Department of Automation and Telemechanics Perm National Research Polytechnic University (614990, Perm, 29, Komsomolsky pr., e-mail: tyurinsergfeo@yandex.ru).

Получено 12.12.2014