2013 Электротехника, информационные технологии, системы управления

No 7

УДК 519.1(075.8)+510.6(075:8)

## $C.\Phi$ . Тюрин<sup>1</sup>, C.B. Ермаков<sup>1</sup>, A.Ю. Городилов<sup>2</sup>

<sup>1</sup>Пермский национальный исследовательский политехнический университет, г. Пермь, Россия

# СРАВНЕНИЕ МОДЕЛЕЙ ВНЕШНИХ ОТКАЗОВ ЭЛЕМЕНТАРНОГО МУЛЬТИПЛЕКСОРА ЛОГИЧЕСКОГО ЭЛЕМЕНТА ПЛИС FPGA ОТНОСИТЕЛЬНО ПОКРЫВАЮЩИХ ТЕСТОВЫХ НАБОРОВ

Рассматривается тестирование элементарного мультиплексора — селектора MS 2-1, составляющего основу логических элементов конфигурируемых логических блоков программируемых логических схем ПЛИС типа FPGA (field-programmable gate array). Рассматриваются модели однократных константных отказов (stuck- at fault), замыканий (bridging fault): «монтажное И, ИЛИ» (wired AND, OR), доминантные замыкания (dominant, dominant AND, OR). Определяются контрольные и диагностические тесты. Показано, что совокупность тестовых наборов относительно однократных внешних константных отказов является таковой и относительно внешних замыканий. Полученные тесты содержат либо одну единицу в наборе (001,010), либо один ноль: 101,110, что позволяет использовать этот факт для построения тестовых наборов для КЛБ реальной размерности. Кроме того, полученное множество тестов оказалось достаточным и для различения всех рассмотренных отказов, то есть для диагностирования, определения вида отказа.

**Ключевые слова:** программируемая логическая интегральная схема (ПЛИС), логический элемент ЛЭ, мультиплексор – селектор MS 2-1, однократные константные отказы, замыкания, доминантные замыкания, монтажное И, ИЛИ, таблица функций отказов, тестовые наборы.

## S.F. Tyurin $^1$ , S.V. Ermakov $^1$ , A.Yu. Gorodilov $^2$

<sup>1</sup>Perm National Research Polytechnic University, Perm, Russian Federation <sup>2</sup>Perm State National Research University, Perm, Russian Federation

## EXTERNAL FAULT MODELS COMPARISON OF FPGA PLIC LOGIC GATE MULTIPLEXER WITH RESPECT TO COVERING TEST SETS

In this paper testing the elementary multiplexer, MS 2-1 selector forming the basis of configurated logic block gates of programmable logic circuits (FPGA type) has been considered. Models of single stuck – at faults, bridging faults: wired AND, OR, dominant, dominant AND, OR have been examined. Also, check and djagnostic tests have been defined. It has been shown that the aggregation of test sets related to single external stuck-at faults is the same as the aggregation of test sets related to external bridging faults. The tests received contain either a single one in the set (001, 010) or a single zero:

<sup>&</sup>lt;sup>2</sup>Пермский государственный национальный исследовательский университет, г. Пермь, Россия

101, 110, that allows us to use this fact to construct test sets for configurated logic blocks of real dimension. Moreover, a great number of tests received proved to be sufficient to disfinguish all the faults considered that is for diagnostics and determination of all fault types.

**Keywords:** programmable logic integrated circuits (PLIC), logic gate, multiplexer, MS 2-1 selector, single stuck-at faults, bridging faults, dominant, dominant AND, OR; wired AND, OR, fault functions table, test sets.

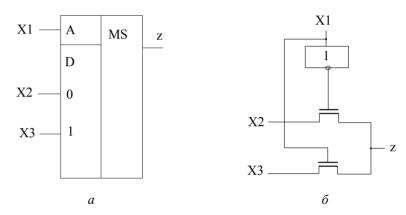

Основой логических элементов (ЛЭ) конфигурируемых логических блоков (КЛБ) ПЛИС типа FPGA (field-programmable gate array) являются мультиплексоры в виде деревьев передающих МОП-транзисторов [1]. Рассмотрим условное графическое обозначение (УГО) элементарного мультиплексора – селектора на 2 канала – MS 2-1 (рис. 1).

Рис. 1. Мультиплексор селектор MS 2-1 на 2 канала: a — УГО элементарного мультиплексора — селектора на 2 канала;  $\delta$  — реализация на передающих МОП-транзисторах без выходного инвертора

Такой мультиплексор относительно внешних входов описывается логической функцией трёх аргументов:

$$z = \bar{x}_1 x_2 \vee x_1 x_3. \tag{1}$$

Сравним модели внешних константных отказов и отказов типа замыканий такого элементарного мультиплексора относительно покрывающих тестовых наборов. Выдвинем гипотезу о том, что существует общее минимальное покрытие, обнаруживающее и те и другие однократные отказы.

### Модель однократных константных отказов

Рассмотрим однократные константные отказы входов мультиплексора 2-1 [2].

При константном отказе адресного входа X1=0:

$$z(x_1 = 0) = \overline{x_1} x_2 \vee x_1 x_3 = \overline{0} \cdot x_2 \vee 0 \cdot x_3 = x_2.$$

(2)

При константном отказе адресного входа X1=1:

$$z(x_1 = 1) = \bar{x}_1 x_2 \lor x_1 x_3 = \bar{1} \cdot x_2 \lor 1 \cdot x_3 = x_3.$$

(3)

При константном отказе входа данных X2=0:

$$z(x_2 = 0) = \overline{x_1} x_2 \vee x_1 x_3 = \overline{x_1} \cdot 0 \vee x_1 \cdot x_3 = x_1 x_3. \tag{4}$$

При константном отказе входа данных X2=1:

$$z(x_2 = 1) = \overline{x_1} x_2 \lor x_1 x_3 = \overline{x_1} \cdot 1 \lor x_1 \cdot x_3 = \overline{x_1} \lor x_3.$$

(5)

При константном отказе входа данных X3=0:

$$z(x_3 = 0) = \overline{x_1}x_2 \lor x_1x_3 = \overline{x_1}x_2 \lor x_1 \cdot 0 = \overline{x_1}x_2.$$

(6)

При константном отказе входа данных X3=1:

$$z(x_3 = 1) = \overline{x_1}x_2 \lor x_1x_3 = \overline{x_1}x_2 \lor x_1 \cdot 1 = x_1 \lor x_2. \tag{7}$$

Получим таблицу функций однократных константных отказов входов (рис. 2).

| константны | е отказы |    |    |     | T1 T2 T5<br>T6 |          |          |          |          |          |

|------------|----------|----|----|-----|----------------|----------|----------|----------|----------|----------|

| T          | X1       | X2 | Х3 | Z   | Z (X1=0)       | Z (X1=1) | Z (X2=0) | Z (X2=1) | Z (X3=0) | Z (X3=1) |

| T0         | 0        | 0  | 0  | 0   | 0              | 0        | 0        | [1]      | 0        | 0        |

| T1         | 0        | 0  | 1  | 0   | 0              | [1]      | 0        | [1]      | 0        | 0        |

| T2         | 0        | 1  | 0  | 1   | 1              | [0]      | [0]      | 1        | 1        | 1        |

| T3         | 0        | 1  | 1  | 1   | 1              | 1        | [0]      | 1        | 1        | 1        |

| T4         | 1        | 0  | 0  | 0   | 0              | 0        | 0        | 0        | 0        | [1]      |

| T5         | 1        | 0  | 1  | 1   | [0]            | 1        | 1        | 1        | [0]      | 1        |

| T6         | 1        | 1  | 0  | 0   | [1]            | 0        | 0        | 0        | 0        | [1]      |

| T7         | 1        | 1  | 1  | . 1 | 1              | 1        | 1        | 1        | [0]      | 1        |

Рис. 2. Таблица функций однократных константных отказов входов

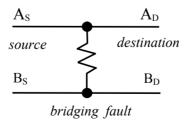

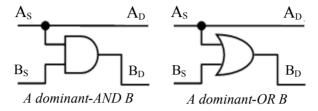

Рис. 3. Модель отказов типа «замыкание» A, B

Очевидно, что в таблице (см. рис. 2) ядра нет — нет столбцов с одной меткой. Таким образом, можно визуально получить, например, покрытие  $T1 \cdot T2 \cdot T5 \cdot T6$ .

К такой модели можно свести и отказы внутренних передающих МОП-транзисторов – «постоянно открыт», «постоянно закрыт».

### Модель однократных отказов-замыканий

Рассмотрим однократные отказы-замыкания внешних входов мультиплексора 2-1 [3, 4] (рис. 3).

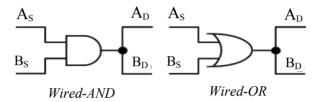

Такая модель включает вариант «монтажное И», «монтажное ИЛИ» [4] (рис. 4).

Рис. 4. Модель отказов типа «монтажное И», «монтажное ИЛИ» А, В

## Монтажное И (wired AND)

В этом случае:

$(x_i)$  wired &  $(x_j)$

$(x_1)$  wired &  $(x_2)$

$$z = \overline{x_1}x_2 \lor x_1x_3 \Longrightarrow \overline{(x_1x_2)}(x_1x_2) \lor (x_1x_2)x_3 = (\overline{x_1} \lor \overline{x_2})x_1x_2 \lor x_1x_2x_3.$$

(8)

$(x_1)$  wired &  $(x_3)$

$$z = \overline{x_1} x_2 \lor x_1 x_3 \Rightarrow \overline{(x_1 x_3)} x_2 \lor (x_1 x_3) x_3 = (\overline{x_1} \lor \overline{x_3}) x_2 \lor x_1 x_3 = (\overline{x_1} \lor \overline{x_2}) x_2 \lor x_1 x_3 = (\overline{x_1} \lor \overline{x_2}) x_2 \lor x_1 x_3.$$

(9)

$(x_2)$ wired &  $(x_3)$

$$z = \overline{x_1} x_2 \lor x_1 x_3 \Rightarrow \overline{(x_1)} x_2 x_3 \lor x_1 (x_2 x_3) = \overline{x_1} x_2 x_3 \lor x_1 x_2 x_3. \tag{10}$$

## Монтажное ИЛИ (wired OR)

При этом:

$(x_i)$  wired  $OR(x_i)$

$(x_1)$ wired  $\vee (x_2)$

$$z = \overline{x_1 x_2} \vee x_1 x_3 \Rightarrow \overline{(x_1 \vee x_2)}(x_1 \vee x_2) \vee (x_1 \vee x_2) x_3 = x_1 x_3 \vee x_2 x_3. \tag{11}$$

$$(x_1) \text{wired} \lor (x_3)$$

$$z = \overline{x_1 x_2} \lor x_1 x_3 \Rightarrow \overline{(x_1 \lor x_3)} x_2 \lor (x_1 \lor x_3) (x_1 \lor x_3) =$$

$$= \overline{x_1 x_2} x_3 \lor x_1 \lor x_3 = x_1 \lor x_2 \lor x_3.$$

(12)

$$(x_{2}) \text{wired} \lor (x_{3})$$

$$z = \overline{x_{1}}x_{2} \lor x_{1}x_{3} \Rightarrow \overline{x_{1}}(x_{2} \lor x_{3}) \lor x_{1}(x_{2} \lor x_{3}) =$$

$$= \overline{x_{1}}x_{2} \lor \overline{x_{1}}x_{3} \lor x_{1}x_{2} \lor x_{1}x_{3} = x_{2} \lor x_{3}.$$

(13)

Получим таблицы функций отказов «монтажное И», «монтажное ИЛИ» (рис. 5).

| Монтажное | И   |    |    |   |         |          |         |

|-----------|-----|----|----|---|---------|----------|---------|

| Т         | X1  | X2 | Х3 | Z | (X1&X2) | Z(X1X3)  | Z (X2X3 |

| T0        | 0   | 0  | 0  | 0 | 0       | 0        | 0       |

| T1        | 0   | 0  | 1  | 0 | 0       | 0        | 0       |

| T2        | 0   | 1  | 0  | 1 | [0]     | 1        | [0]     |

| T3        | 0   | 1  | 1  | 1 | [0]     | 1        | 1       |

| T4        | 1   | 0  | 0  | 0 | 0       | 0        | 0       |

| T5        | 1   | 0  | 1  | 1 | [0]     | 1        | [0]     |

| T6        | 1   | 1  | 0  | 0 | 0       | [1]      | 0       |

| T7        | 1   | 1  | 1  | 1 | 1       | 1        | 1       |

| Монтажное | или |    |    |   |         |          |         |

| Т         | X1  | X2 | Х3 | Z | (X1uX2) | Z(X1uX3) | Z(X2uX3 |

| TO        | 0   | 0  | 0  | 0 | 0       | 0        | 0       |

| T1        | 0   | 0  | 1  | 0 | 0       | [1]      | 1       |

| T2        | 0   | 1  | 0  | 1 | [0]     | 1        | [1]     |

| T3        | 0   | 1  | 1  | 1 | 1       | 1        | 1       |

| T4        | 1   | 0  | 0  | 0 | 0       | [1]      | 0       |

| T5        | 1   | 0  | 1  | 1 | 1       | 1        | 1       |

| T6        | 1   | 1  | 0  | 0 | 0       | [1]      | [1]     |

| T7        | 1   | 1  | 1  | 1 | 1       | 1        | 1       |

Рис. 5. Таблица функций однократных отказов замыканий «монтажное И», «монтажное ИЛИ»

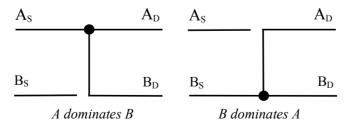

Рассмотрим доминантные замыкания:

Доминантное замыкание (Dominant) (рис. 6).

Рис. 6. Доминантные замыкания

Таким образом,  $(x_i)$ Dominant $(x_i)$ .

Так, при  $(x_1)$ Dominant $(x_2)$

$$z = \overline{x_1} x_2 \lor x_1 x_3 \Longrightarrow \overline{x_1} x_1 \lor x_1 x_3 = x_1 x_3. \tag{14}$$

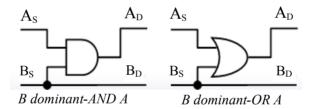

Доминантное И (Dominant) (рис. 7).

Рис. 7. Доминантное И

Следовательно,  $(x_i)$ Dominant $(x_i & x_j)$ .

Так, при  $(x_1)$ Dominant $(x_1 & x_2)$

$$z = \overline{x_1} x_2 \lor x_1 x_3 \Rightarrow \overline{x_1} (x_1 x_2) \lor x_1 x_3 = x_1 x_3.$$

(15)

Доминантное ИЛИ (Dominant) (рис. 8).

Рис. 8. Доминантное ИЛИ

Поэтому  $(x_i)$ Dominant $(x_i \lor x_j)$ .

Так, при  $(x_1)$ Dominant $(x_1 \lor x_2)$

$$z = \overline{x_1} x_2 \lor x_1 x_3 \Longrightarrow \overline{x_1} (x_1 \lor x_2) \lor x_1 x_3 = \overline{x_1} x_2 \lor x_1 x_3.$$

(16)

Получим таблицы функций доминантных отказов (рис. 9).

## Определение контрольных тестов

Получим конъюнктивное покрытие [5] таблиц функций отказов (рис. 2, 5, 9):

– для рис. 2:

$$(T5 \lor T6)(T1 \lor T2)(T2 \lor T3) (T0 \lor T1) (T5 \lor T7) (T2 \lor T3) (T4 \lor T6).$$

(17)

| Доминанта       |    | (Xi_D_Xj)=> | Xi=Xi; Xj=Xi  |      | T1 T2 T5<br>T6 |           |           |           |           |          |

|-----------------|----|-------------|---------------|------|----------------|-----------|-----------|-----------|-----------|----------|

|                 |    |             |               |      |                |           | Оши       | бки       |           |          |

| T               | X1 | X2          | Х3            | Z    | (X1_D_X2)      | (X1_D_X3) | (X2_D_X1) | (X2_D_X3) | (X3_D_X1) | (X3_D_X2 |

| TO TO           | 0  | 0           | 0             | 0    | - 8            |           |           |           |           |          |

| T1              | 0  | 0           | 1             | 0    |                |           |           |           | 1         | 1 0      |

| T2              | 0  | 1           | 0             | 1    | 0              |           | 0         |           |           | 0        |

| T3              | 0  | 1           | 1             | 1    | 0              |           |           |           |           |          |

| T4              | 1  | 0           | 0             | 0    |                | 1         |           |           |           |          |

| T5              | 1  | 0           | 1             | 1    |                |           | <u>o</u>  | 0 1       |           |          |

| T6              | 1  | 1           | 0             | 0    |                | 1         |           | 1         | 1         |          |

| T7              | 1  | 1           | 1             | 1    |                | -         |           |           |           |          |

| Доминантное И   |    | (Xi_D_Xj)=> | Xi=Xi; Xj=Xi* | Xj   |                |           |           |           |           |          |

| Т               | X1 | X2          | Х3            | Z    | (X1_D_X2)      | (X1_D_X3) | (X2_D_X1) | (X2_D_X3) | (X3_D_X1) | (X3_D_X2 |

| TO              | 0  | 0           | 0             | 0    |                |           |           | 1         |           |          |

| T1              | 0  | 0           | 1             | 0    |                |           |           |           |           |          |

| T2              | 0  | 1           | 0             | 1    | 0              |           |           | 1         | i i       | 0        |

| T3              | 0  | 1           | 1             | 1    | 0              |           | -:        |           |           |          |

| T4              | 1  | 0           | 0             | 0    |                |           |           |           |           |          |

| T5              | 1  | 0           | 1             | 1    | - 8            |           | 0         | 0         |           |          |

| T6              | 1  | 1           | 0             | 0    |                |           |           |           | 1         |          |

| T7              | 1  | 1           | 1             | 1    |                |           |           |           |           |          |

| Доминантное ИЛИ |    | (Xi_D_Xj)=> | Xi=Xi; Xj=Xi  | V Xj |                |           |           |           |           |          |

| Т               | X1 | X2          | Х3            | Z    | (X1_D_X2)      | (X1_D_X3) | (X2_D_X1) | (X2_D_X3) | (X3_D_X1) | (X3_D_X2 |

| TO              | 0  | 0           | 0             | 0    |                |           |           |           |           |          |

| T1              | 0  | 0           | 1             | 0    |                |           |           |           | 1         | 1        |

| T2              | 0  | 1           | 0             | 1    |                |           | 0         |           | 320       | 350      |

| T3              | 0  | 1           | 1             | 1    |                |           |           |           |           |          |

| T4              | 1  | 0           | 0             | 0    |                | 1         | -:        | -:        |           |          |

| T5              | 1  | 0           | 1             | 1    |                |           |           |           |           |          |

| T6              | 1  | 1           | 0             | 0    |                | 1         |           | 1         |           |          |

| T7              | 1  | 1           | 1             | 1    |                |           | 21        | -: D.C.   |           |          |

Рис. 9. Таблицы функций доминантных отказов

Раскрыв 16, например, можно получить покрытие T1T2T5T6 (выделено цветом на рис. 2);

– для рис. 5 – монтажное И:

$$(T2\lor T3\lor T5)T6(T2\lor T5).$$

(18)

Монтажное ИЛИ:

$$T2(T1 \lor T4 \lor T6)(T2 \lor T6).$$

(19)

– для рис. 9 – доминанта:

$$T2T6(T2\lor T5) (T5\lor T6) (T1\lor T6) (T1\lor T2).$$

(20)

Доминантное И:

$$T2T5T6.$$

(21)

Доминантное ИЛИ:

Анализ (18)–(22) позволяет сделать вывод о том, что покрытие T1T2T5T6 также является контрольным тестом для отказов-замыканий. Обратим внимание, что тесты T1, T2 содержат одну единицу в наборе (001,010), а тесты T5,T6 – один ноль: 101,110.

## Определение диагностических тестов

Попробуем проверить ещё одну гипотезу о том, что полученное множество тестов достаточно для различения всех рассмотренных отказов. Построим таблицу различения однократных константных отказов входов (рис. 10).

| т         | (X1=0) | (X1=0) | (X1=0) | (X1=0) | (X1=0) | (X1=1) | (X1=1) | (X1=1) | (X1=1) | (X2=0) | (X2=0) | (X2=0) | (X2=1) | (X2=1) | (X3=0) |

|-----------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| 1         | (X1=1) | (X2=0) | (X2=1) | (X3=0) | (X3=1) | (X2=0) | (X2=1) | (X3=0) | (X3=1) | (X2=1) | (X3=0) | (X3=1) | (X3=0) | (X3=1) | (X3=1) |

| T0        |        |        | [1]    |        |        |        | [1]    |        |        | [1]    |        |        | [1]    | [1]    |        |

| <b>T1</b> | [1]    |        | [1]    |        |        | [1]    |        | [1]    | [1]    | [1]    |        |        | [1]    | [1]    |        |

| <b>T2</b> | [0]    | [0]    |        |        |        |        | [0]    | [0]    | [0]    | [0]    | [0]    | [0]    |        |        |        |

| T3        |        | [0]    |        |        |        | [0]    |        |        |        | [0]    | [0]    | [0]    |        |        |        |

| T4        |        |        |        |        | [1]    |        |        |        | [1]    |        |        | [1]    |        | [1]    | [1]    |

| T5        | [0]    | [0]    | [0]    |        | [0]    |        |        | [0]    |        |        | [0]    |        | [0]    |        | [0]    |

| <b>T6</b> | [1]    | [1]    | [1]    | [1]    |        |        |        |        | [1]    |        |        | [1]    |        | [1]    | [1]    |

| T7        |        |        |        | [0]    |        |        |        | [0]    |        |        | [0]    |        | [0]    |        | [0]    |

Рис. 10. Таблица различения однократных константных отказов входов

Видим, что для этого вида отказов множество тестов T1, T2, T5, T6 достаточно для различения всех рассмотренных пар отказов.

Для отказов типа «монтажное И, ИЛИ» (рис. 11) это покрытие более чем достаточно.

| T               | (X1 X2)<br>(X1 X3) | (X1 X2)<br>(X2 X3) | (X1 X3)<br>(X2 X3) | (X1∨X2)<br>(X1∨X3) | (X1∨X2)<br>(X2∨X3) | (X1∨X3)<br>(X2∨X3) |

|-----------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| T0              |                    |                    |                    |                    |                    |                    |

| T1              |                    |                    |                    | [1]                |                    | [1]                |

| T2              | [0]                | [0]                | [0]                | [0]                | [1]                | [1]                |

| T3              | [0]                |                    |                    |                    |                    |                    |

| T4              |                    |                    |                    | [1]                |                    | [1]                |

| T5              | [0]                |                    | [0]                |                    |                    |                    |

| <mark>T6</mark> | [1]                |                    | [1]                | [1]                | [1]                | [1]                |

| T7              |                    |                    |                    |                    |                    |                    |

Рис. 11. Таблица различения однократных константных отказов типа «монтажное И, ИЛИ»

Для доминантных отказов (рис. 12) гипотеза подтверждается.

| T         |     |     |     |     |     |     | (X1DX3)<br>(X2DX3) |     |     |     | (X2DX1)<br>(X3DX1) |     |

|-----------|-----|-----|-----|-----|-----|-----|--------------------|-----|-----|-----|--------------------|-----|

| T0        |     |     |     |     |     |     |                    |     |     |     |                    |     |

| T1        |     |     |     |     | [1] |     |                    | [1] | [1] |     | [1]                | [1] |

| T2        | [0] |     | [0] | [0] |     | [0] |                    |     | [0] | [0] | [0]                |     |

| T3        | [0] | [0] | [0] | [0] | [1] |     |                    |     |     |     |                    |     |

| T4        | [1] |     |     |     |     | [1] | [1]                | [1] | [1] |     |                    |     |

| T5        |     | [0] | [0] |     |     | [0] | [0]                |     |     |     | [0]                | [0] |

| <b>T6</b> | [1] |     | [1] | [1] |     | [1] |                    |     | [1] | [1] | [1]                |     |

| T7        |     |     |     |     |     |     |                    |     |     |     |                    |     |

Рис. 12. Таблица различения доминантных отказов

| -         | (X2DX3)            | (X2DX3)            | (X3DX1)            |

|-----------|--------------------|--------------------|--------------------|

| T         | (X2DX3)<br>(X3DX1) | (X2DX3)<br>(X3DX2) | (X3DX1)<br>(X3DX2) |

| T0        |                    |                    |                    |

| <b>T1</b> |                    | [1]                |                    |

| <b>T2</b> |                    | [0]                | [0]                |

| T3        |                    |                    |                    |

| T4        |                    |                    |                    |

| <b>T5</b> | [0]                | [0]                |                    |

| <b>T6</b> | [1]                | [1]                | [1]                |

| T7        |                    |                    |                    |

Рис. 12. Окончание

Для доминантного И, ИЛИ (см. рис. 9) имеется по одному случаю, когда отказ не влияет на работоспособность устройства ((X1D&X3), (X1D $\vee$ X2)), и по одному случаю, когда отказы не различаются ([(X2D&X1), (X2D&X3)], [(X3D $\vee$ X1), (X3D $\vee$ X2)]). В случае неразличения отказов реализуются одинаковые функции, и их парирование в смысле [6–12] будет в принципе аналогичным. Легко видеть, что все метки для доминантного И, ИЛИ (см. рис. 9) лежат в зоне указанных тестовых наборов.

Таким образом, выдвинутая гипотеза о том, что совокупность проверяющих тестовых наборов (контрольного теста) относительно однократных внешних константных отказов является таковой и относительно внешних замыканий. Полученные тесты содержат либо одну единицу в наборе (001,010), либо один ноль (101,110). Кроме того, полученное множество тестов оказалось достаточным и для различения всех рассмотренных отказов, то есть для диагностирования, определения вида отказа. В дальнейшем целесообразно автоматизировать процедуру построения таблиц функций отказов и конъюнктивных покрытий, рассмотреть случай различения различных типов пар отказов между собой. Целесообразно также предложить процедуру, упрощающую нахождение тестовых наборов для мультиплексоров, имеющих n=4,5,6,7 и более адресных входов, когда общее число переменных тестирования S определяется как  $S=n+2^n(21)$ .

## Библиографический список

- 1. Цыбин С. Программируемая коммутация ПЛИС: взгляд изнутри [Электронный ресурс]. URL: http://www.kit-e.ru/articles/plis/2010 11 56.php (дата обращения: 01.01.2013).

- 2. Stuck-at fault [Электронный ресурс]. URL: http://en.wikipedia.org/wiki/Stuck-at fault (дата обращения: 27.09.2013).

- 3. Bridging fault [Электронный ресурс]. URL: http://en.wikipedia.org/wiki/Bridging fault (дата обращения: 28.09.2013).

- 4. Тюрин С.Ф., Греков А.В., Громов О.А. Определение функционально-полных толерантных булевых функций четырёх аргументов с учётом модели замыканий переменных // Доклады Академии военных наук. Саратов, 2011. №5 (49). С. 35–44.

- 5. Тюрин С.Ф., Громов О.А. Разработка контрольных и диагностических тестов для КМОП-элементов с избыточным базисом // Научно-практический журнал «Приволжский научный вестник». 2013. 1000 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 100 —

- 6. Тюрин С.Ф. Синтез адаптируемой к отказам цифровой аппаратуры с резервированием базисных функций // Приборостроение. -1999. № 1. C. 36–39.

- 7. Тюрин С.Ф. Адаптация к отказам одновыходных схем на генераторах функций с функционально-полными толерантными элементами // Приборостроение. 1999. № 7. С. 32–34.

- 8. Адаптация FPGA до відмови логіки / С.Ф. Тюрін, О.А. Громов, А.В. Греков, І.С. Понуровскій // Радіоелектронні і комп'ютерні системы. -2013. -№ 1(60). -С. 177–182.

- 9. Тюрин С.Ф., Громов О.А., Понуровский И.С. Адаптация к отказам программируемых логических схем FPGA // Вестник Международ. ун-та им. С.Ю. Витте. Сер. 1: Экономика и управление: материалы XLI междунар. конф. «Информационные технологии в науке, образовании, телекоммуникации и бизнесе». Майская сессия; Украина, Крым, Ялта-Гурзуф, 25 мая—4 июня 2013 г. М., 2013. С. 111—114.

- 10. Городилов А.Ю., Понуровскій І.С., Тюрін С.Ф. Повышение отказоустойчивости FPGA путём реконфигурации работоспособных элементов // Радіоелектронні і комп'ютерні системы. — 2013. — № 1(60). — С. 172—176.

- 11. Тюрин С.Ф., Громов О.А., Каменских А.Н. Программный комплекс исследования методов повышения надежности // Вестник Ижевск. гос. техн. ун-та. -2012. N $_2$ . C. 153-156.

- 12. Тюрин С.Ф., Греков А.В., Коржев В. С. Скользящее резервирование с восстановлением на основе элементов с избыточным базисом // Научно-технические ведомости Санкт-Петербург. гос. политехн. ун-та. -2012.- № 5(157).- C. 38-44.

### Сведения об авторах

**Тюрин Сергей Феофентович** (Пермь, Россия) — заслуженный изобретатель Российской Федерации, доктор технических наук, профессор кафедры автоматики и телемеханики, Пермского национального исследовательского политехнического университета (614990, Пермь, Комсомольский пр., 29, e-mail: tyurinsergfeo@yandex.ru).

**Ермаков Сергей Вячеславович** (Пермь, Россия) – магистрант кафедры автоматики и телемеханики Пермского национального исследовательского политехнического университета (614990, Пермь, Комсомольский пр., 29, e-mail: yermakovsergey@gmail.com).

**Городилов Алексей Юрьевич** (Пермь, Россия) — старший преподаватель кафедры математического обеспечения вычислительных систем Пермского государственного национального исследовательского университета, e-mail: gora830@yandex.ru).

#### About the authors

**Tyurin Sergey Feofentovich** (Perm, Russian Federation) an honoured inventor of the Russia Federation, Doctor of technical sciences, professor at the department of automatics and telemechanics of Perm National Research Polytechnic University (614990, Perm, 29, Komsomolsky pr., e-mail: tyurinsergfeo@yandex.ru).

**Ermakov Sergey Vyacheslavovich** (Perm, Russian Federation), master's degree student at the department of the automatics and telemechanics of Perm National Research Polytechnic University (614990, Perm, 29, Komsomolsky pr., e-mail: yermakovsergey@gmail.com).

**Gorodilov Alexey Yuryevich** (Perm, Russian Federation), assistant lecturer at the department of computer system software of Perm State National Research University (e-mail: gora830@yandex.com).

Получено: 05.09.2013